# **2006 Electronic Edition**

# Clifton G. Fonstad

Department of Electrical Engineering and Computer Science Massachusetts Institute of Technology

Copyright © 2006 by Clifton G. Fonstad. All rights reserved.

# **Microelectronic Devices and Circuits, 2006 Electronic Edition**

Copyright © 2006 by Clifton G. Fonstad. All rights reserved.

Published under Creative Commons License 2.5, which is available at http://creativecommons.org/licenses/by-nc-nd/2.5/

• You are free to copy, distribute, display, and perform the work under the following conditions:

<u>Attribution</u> - You must attribute the work indicating the title is "Microelectronic Devices and Circuits, 2006 Electronic Edition" and that it has been authored, published, copyrighted, and licensed by Clifton G. Fonstad.

Noncommercial - You may not use this work for commercial purposes.

- No Derivative Works You may not alter, transform, or build upon this work.

- For any reuse or distribution, you must make clear to others the license terms of this work.

- Any of these conditions can be waived if you get permission from the copyright holder.

- Your fair use and other rights are in no way affected by the above.

- This is a human-readable summary of the Legal Code; the full license can be viewed at

http://creativecommons.org/licenses/by-nc-nd/2.5/legalcode

# Notes:

This book is based on the textbook Microelectronic Devices and Circuits by Clifton G. Fonstad, which was published by McGraw-Hill in 1994. The Library of Congress cataloging-in-publication data for that book is reproduced below:

Fonstad, Clifton G.

Microelectronic devices and circuits / Clifton G. Fonstad

p. cm. – (McGraw-Hill series in electrical and computer engineering. Electronics and VLSI circuits.)

Includes index.

ISBN 0-07-021496-4

1. Microelectronics. 2. Electric circuit analysis. 3. Electric circuits, Nonlinear. I. Title. II. Series

TK 7874.F645 1994

621.381-dc20 93-3250

McGraw-Hill has declared the original textbook "out of print" and has transferred the copyright to the author, Clifton G. Fonstad.

Errata in the original text identified as of August 15, 2006 have been corrected in this edition.

This edition will appear enlarged 110% from the original page size when printed on standard letter paper (8.5" x 11").

# CONTENTS

|   | Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ix                                                                         |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 1 | Modeling<br>1.1 General Comments<br>1.2 Empirical Device Models<br>1.3 Why Semiconductors? Why Transistors?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1<br>1<br>3<br>4                                                           |

| 2 | <ul> <li>Uniform Semiconductors in Equilibrium</li> <li>2.1 Thermal Equilibrium</li> <li>2.2 Intrinsic Silicon</li> <li>2.3 Extrinsic Silicon</li> <li>2.3.1 Donors and Acceptors</li> <li>2.3.2 Detailed Balance</li> <li>2.3.3 Equilibrium Carrier Concentration</li> <li>2.4 Additional Semiconductors</li> <li>2.4.1 Elemental Semiconductors</li> <li>2.4.2 Compound Semiconductors</li> <li>2.5 The Effects of Changing Temperature</li> <li>2.6 Summary</li> </ul>                                                                                                                     | 7<br>9<br>14<br>14<br>17<br>21<br>22<br>22<br>22<br>22<br>24<br>25         |

| 3 | <ul> <li>Uniform Excitation of Semiconductors</li> <li>3.1 Uniform Electric Field: Drift</li> <li>3.1.1 Drift Motion and Mobility</li> <li>3.1.2 Drift Current and Conductivity</li> <li>3.1.3 Temperature Variation of Mobility and Conductivity</li> <li>3.2 Uniform Optical Excitation</li> <li>3.2.1 Minority Carrier Lifetime</li> <li>3.2.2 Population Transients</li> <li>3.2.3 High-Level Injection Populations and Transients</li> <li>3.3 Photoconductivity and Photoconductors</li> <li>3.3.1 Basic Concepts</li> <li>3.3.2 Specific Device Issues</li> <li>3.4 Summary</li> </ul> | 31<br>31<br>34<br>37<br>37<br>38<br>40<br>45<br>48<br>48<br>48<br>49<br>53 |

**iv** contents

| 4 | Nonuniform Situations: The Five Basic Equations         | 61  |

|---|---------------------------------------------------------|-----|

|   | 4.1 Diffusion                                           | 61  |

|   | 4.1.1 A Model for Diffusion                             | 62  |

|   | 4.1.2 Diffusion Current Density                         | 63  |

|   | 4.1.3 Other Diffusion Important in Devices              | 63  |

|   | 4.2 Modeling Nonuniform Situations                      | 64  |

|   | 4.2.1 Total Current Densities                           | 64  |

|   | 4.2.2 The Continuity Equations                          | 65  |

|   | 4.2.3 Gauss's Law                                       | 66  |

|   | 4.2.4 The Five Basic Equations                          | 66  |

|   | 4.3 Summary                                             | 67  |

| _ | -                                                       |     |

| 5 | Nonuniform Carrier Injection: Flow Problems             | 71  |

|   | 5.1 Developing the Diffusion Equation                   | 71  |

|   | 5.1.1 Uniformly Doped Extrinsic Material                | 72  |

|   | 5.1.2 Low-Level Injection                               | 72  |

|   | 5.1.3 Quasineutrality                                   | 73  |

|   | 5.1.4 Minority Carriers Flow by Diffusion               | 75  |

|   | 5.1.5 Time-Dependent Diffusion Equation                 | 76  |

|   | 5.1.6 Quasistatic Diffusion: Flow Problems              | 76  |

|   | 5.2 Flow Problems                                       | 78  |

|   | 5.2.1 Homogeneous Solutions                             | 78  |

|   | 5.2.2 Particular Solutions                              | 80  |

|   | 5.2.3 Boundary Conditions                               | 80  |

|   | 5.2.4 The Total Current                                 | 83  |

|   | 5.2.5 Specific Situations                               | 85  |

|   | 5.2.6 The Currents, Electric Field, and Net Charge      | 96  |

|   | 5.3 Summary                                             | 100 |

| 6 | -                                                       |     |

| Ų | Nonuniformly Doped Semiconductors                       |     |

|   | in Thermal Equilibrium                                  | 109 |

|   | 6.1 General Description: The Poisson-Boltzmann Equation | 110 |

|   | 6.2 Gradual Spatial Variation of Doping                 | 113 |

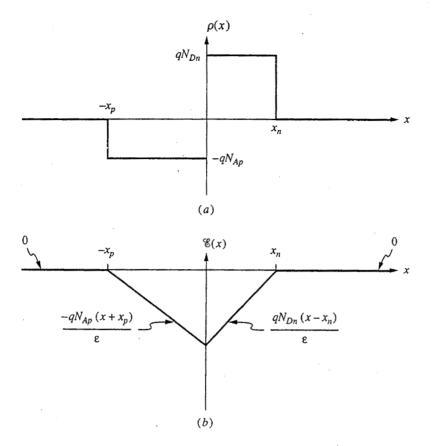

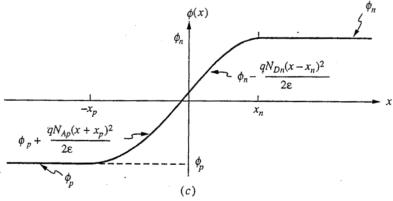

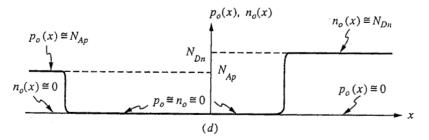

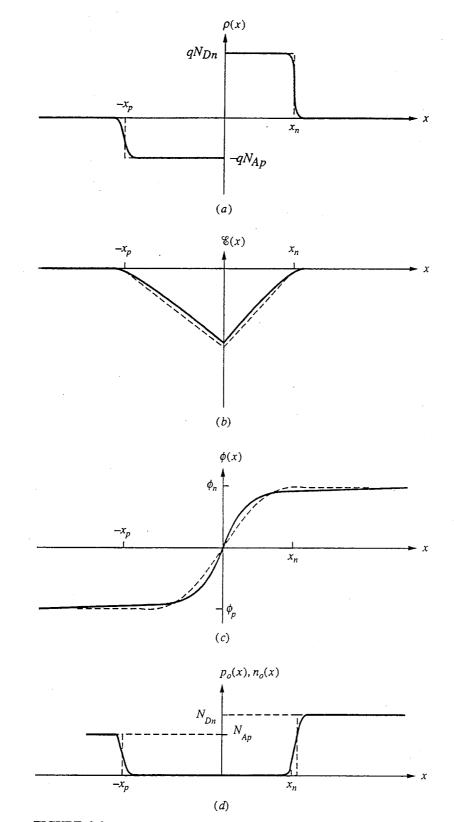

|   | 6.3 <i>p-n</i> Junction: The Depletion Approximation    | 115 |

|   | 6.3.1 Abrupt <i>p</i> - <i>n</i> Junction               | 116 |

|   | 6.3.2 Other <i>p</i> - <i>n</i> Junction Profiles       | 123 |

|   | 6.4 The Electrostatic Potential around a Circuit        | 124 |

|   | 6.5 Summary                                             | 126 |

| 7 | Junction Diodes                                         | 131 |

| ' | 7.1 Applying Voltage to a $p-n$ Junction                | 131 |

|   |                                                         | 131 |

|   | 7.2 Depletion Region Changes                            |     |

|   | 7.2.1 Depletion Width Variation with Voltage            | 134 |

|   | 7.2.2 Depletion Capacitance                             | 134 |

|   | 7.2.3 Applications of the Depletion Capacitance         | 137 |

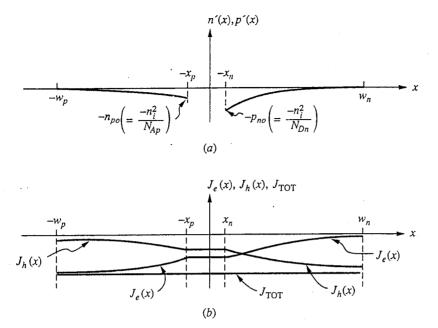

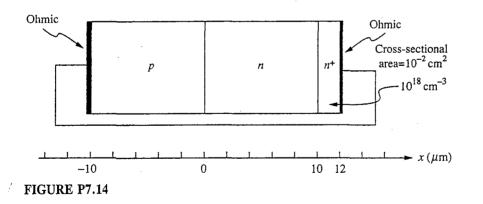

|   | 7.3 Current Flow                                        | 139 |

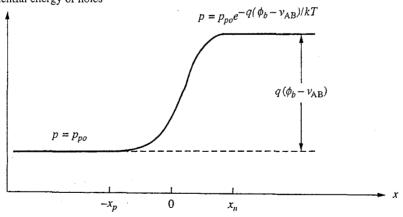

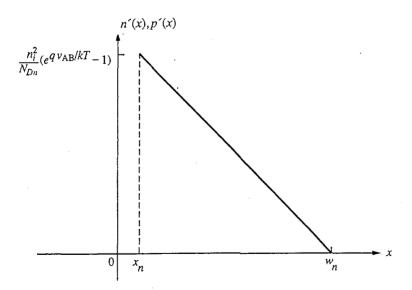

|   | 7.3.1 Excess Populations at the Depletion Region Edges  | 141 |

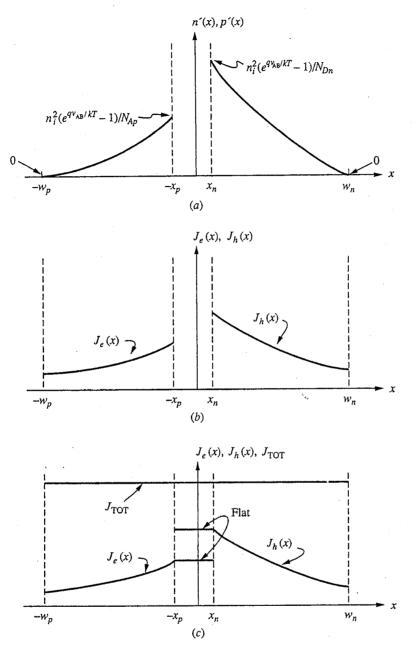

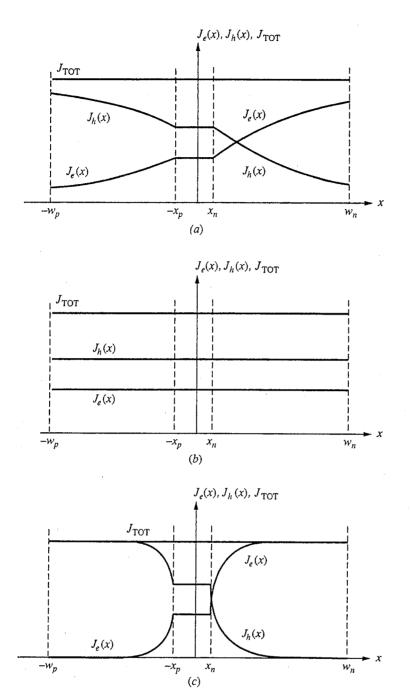

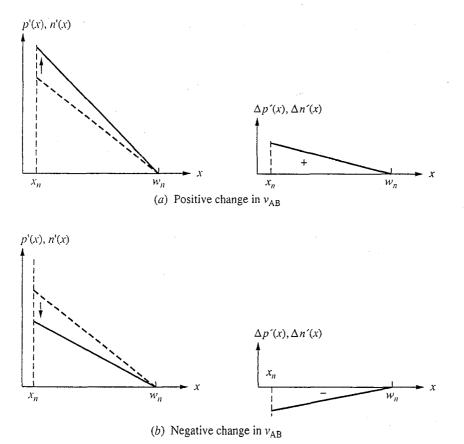

|   | 7.3.2 Current-Voltage Relationship for an Ideal Diode   | 144 |

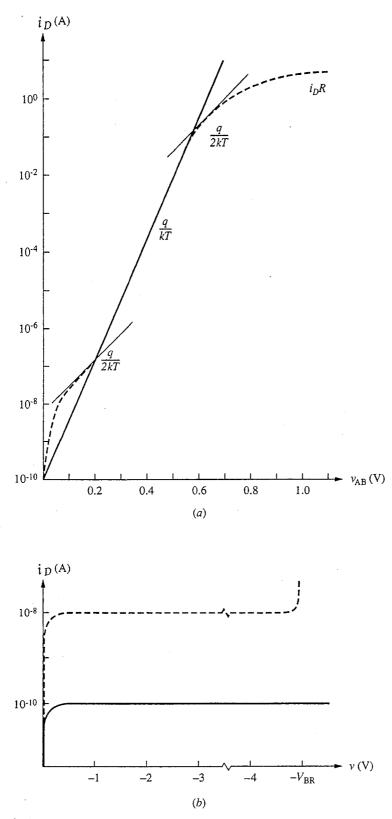

|   | 7.3.3 Limitations to the Simple Model                   | 151 |

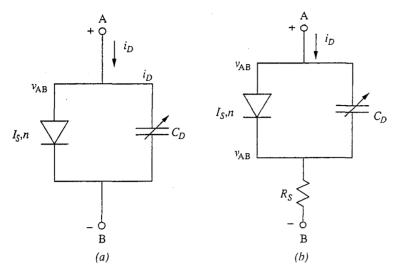

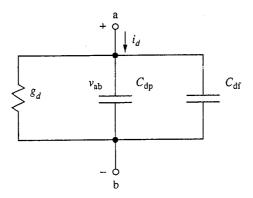

|   | 7.3.4 Diffusion Capacitance                             | 154 |

v

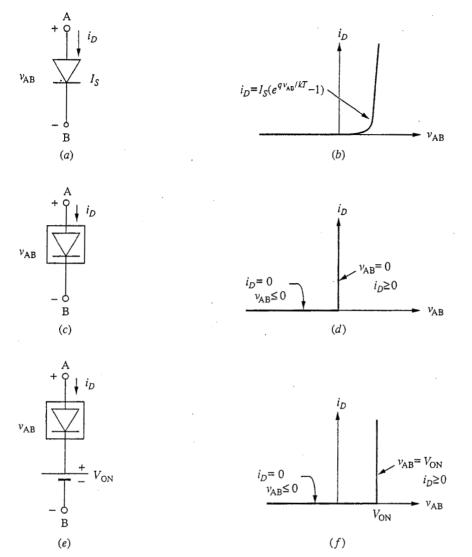

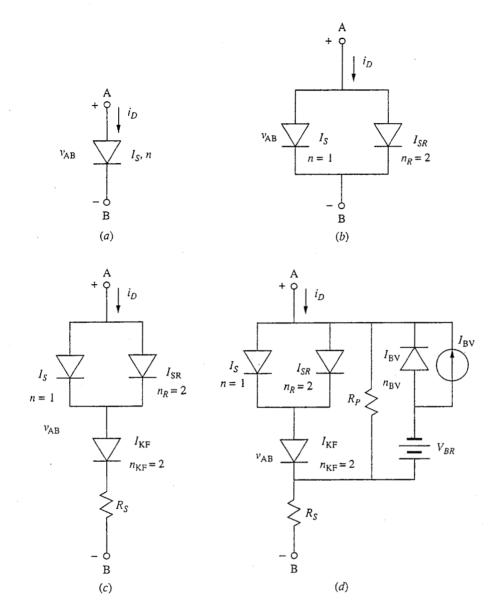

|    | 7.4 Circuit Models for Junction Diodes                                                   | 157 |

|----|------------------------------------------------------------------------------------------|-----|

|    | 7.4.1 Large-Signal Models                                                                | 157 |

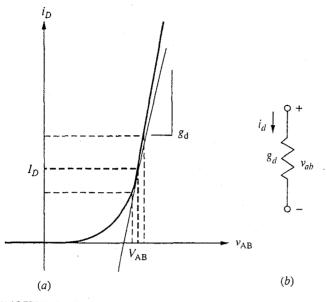

|    | 7.4.2 Static Small-Signal Linear Models                                                  | 162 |

|    | 7.5 Solar Cells and Photodiodes                                                          | 166 |

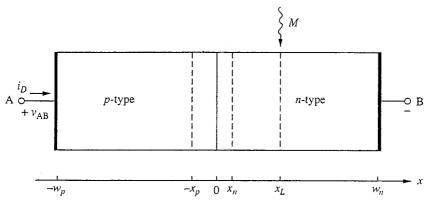

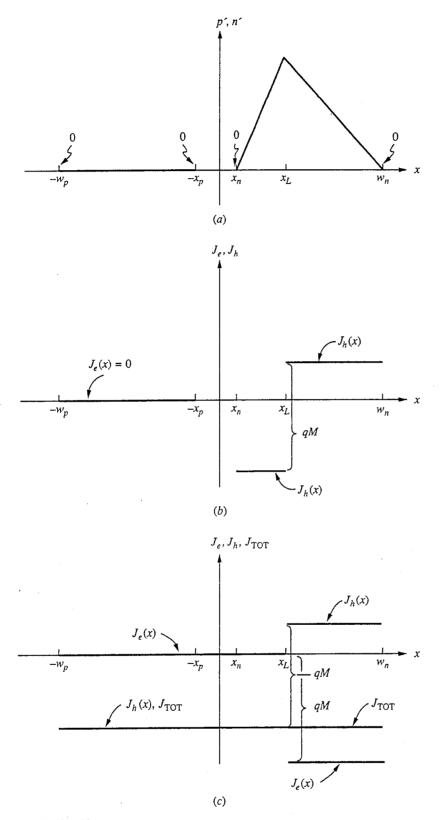

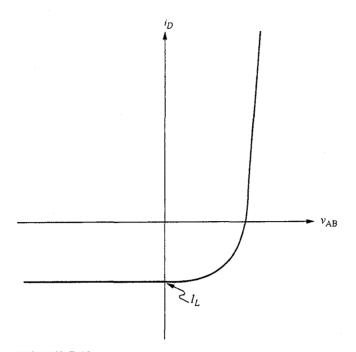

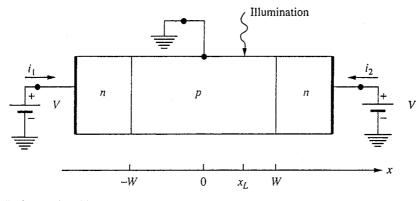

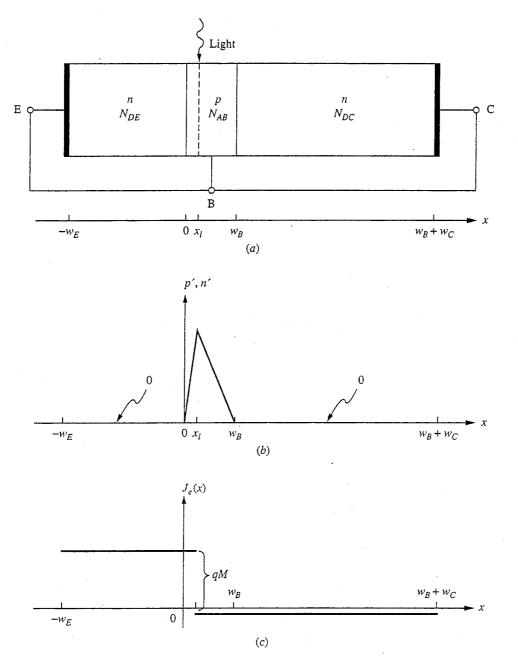

|    | 7.5.1 Optical Excitation of <i>p</i> - <i>n</i> Diodes                                   | 167 |

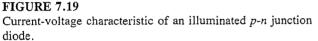

|    | 7.5.2 Applications of Illuminated $p$ - $n$ Diodes                                       | 169 |

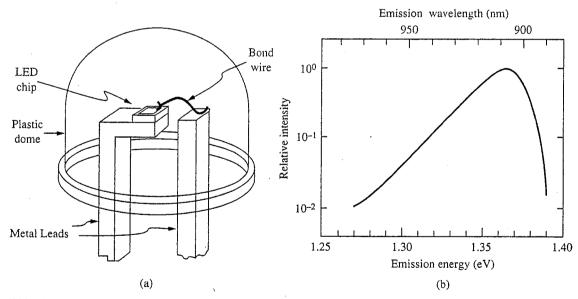

|    | 7.6 Light-Emitting Diodes                                                                | 173 |

|    | 7.7 Summary                                                                              | 174 |

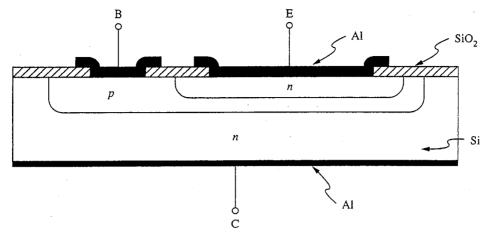

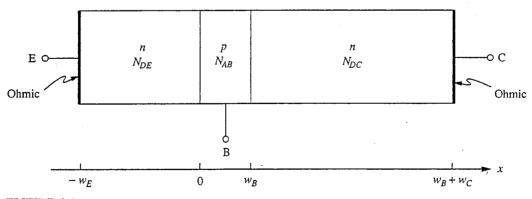

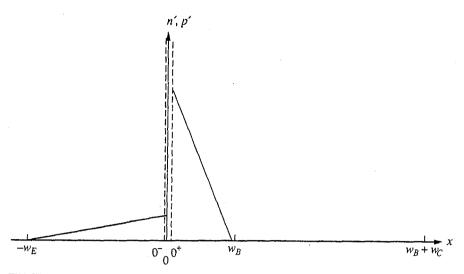

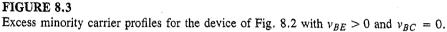

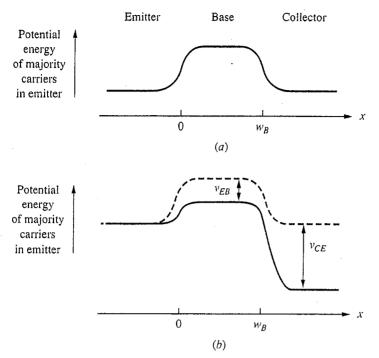

| 8  | Bipolar Junction Transistors                                                             | 185 |

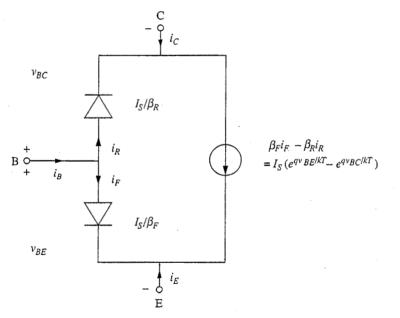

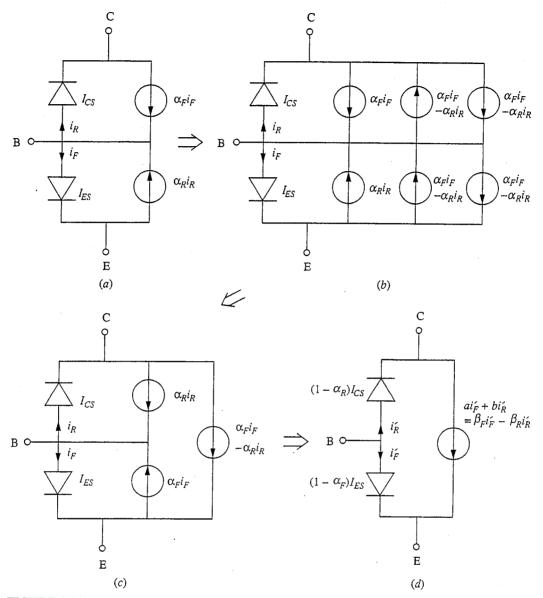

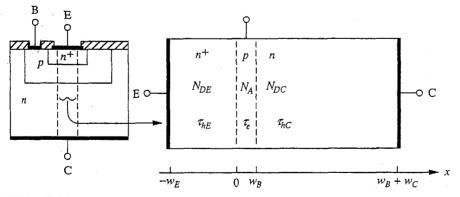

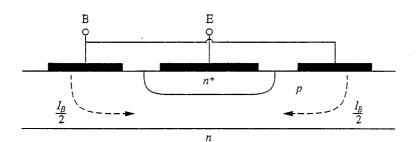

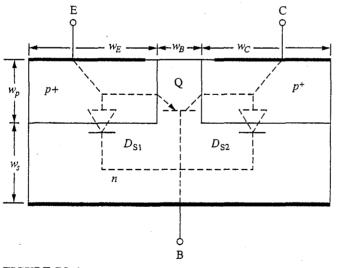

| 0  | 8.1 The Ebers–Moll Model for Uniformly Doped                                             | 105 |

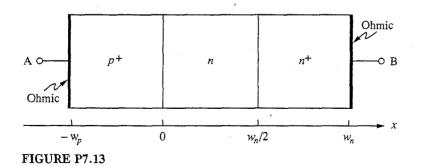

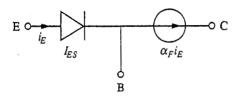

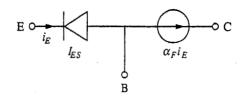

|    | One-Dimensional BJTs                                                                     | 187 |

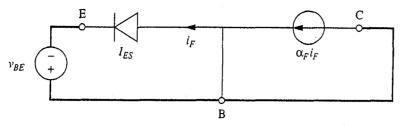

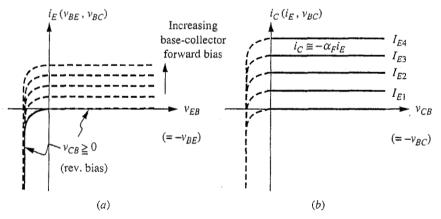

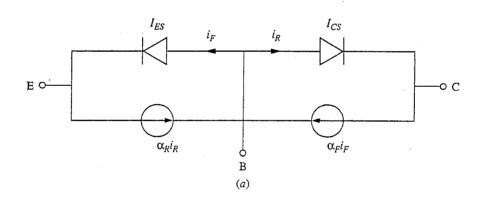

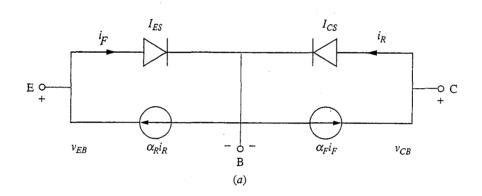

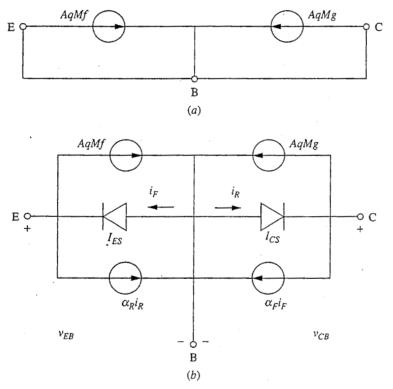

|    | 8.1.1 Superposition                                                                      | 187 |

|    | 8.1.2 The Forward Portion ( $v_{BC} = 0$ )                                               | 188 |

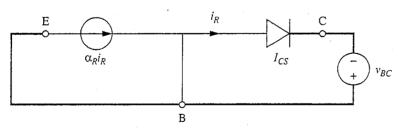

|    | 8.1.2 The roward rotation ( $v_{BC} = 0$ )<br>8.1.3 The Reverse Portion ( $v_{BE} = 0$ ) | 192 |

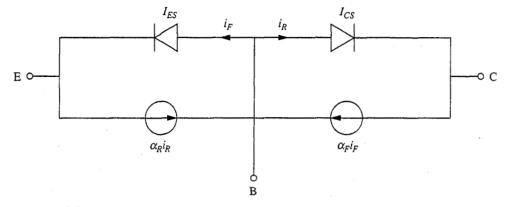

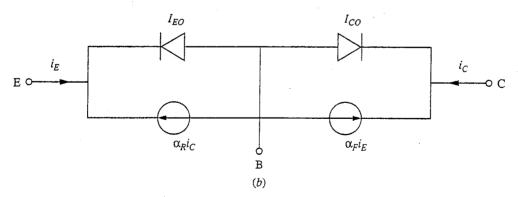

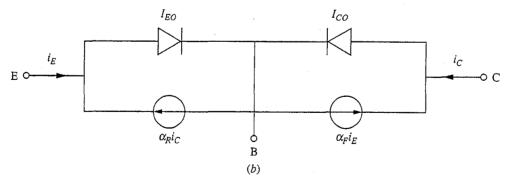

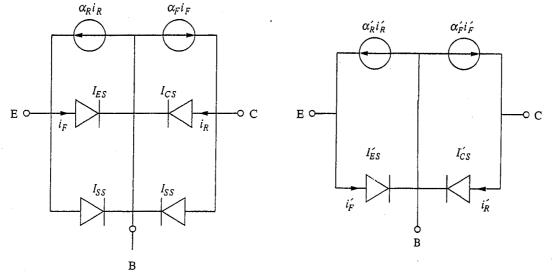

|    | 8.1.4 Full Solution: The Ebers–Moll Model                                                | 192 |

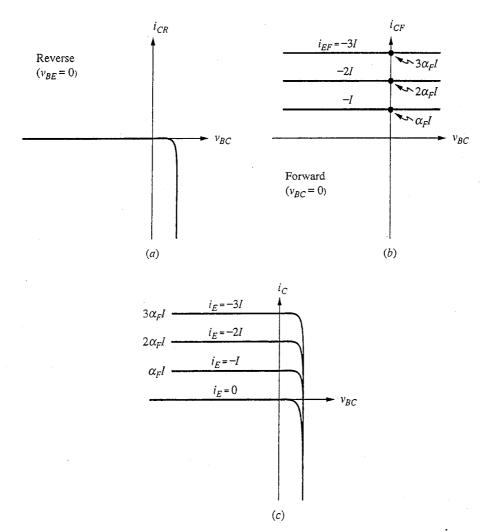

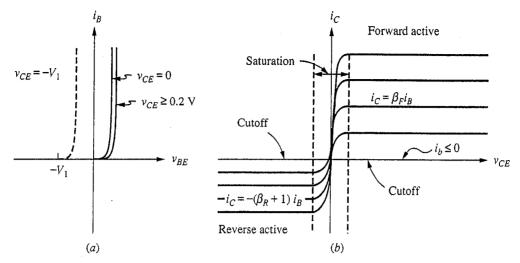

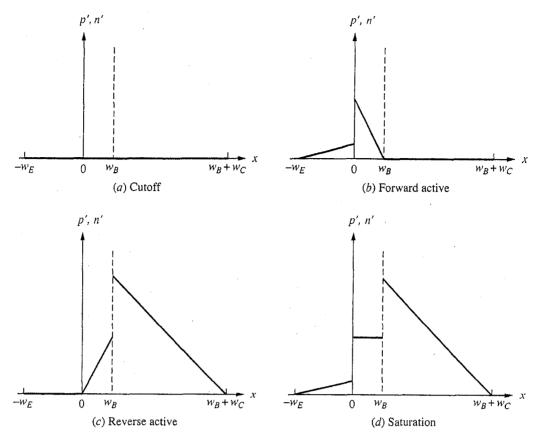

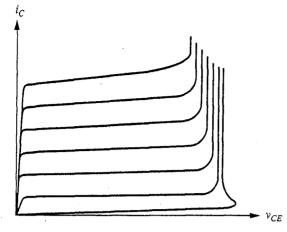

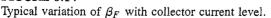

|    | 8.1.5 Characteristics and Operating Regions                                              | 195 |

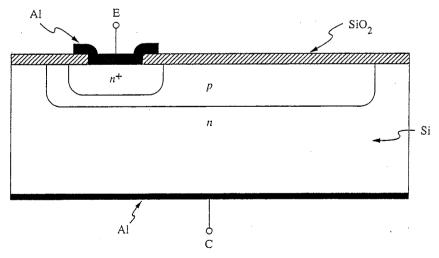

|    | 8.1.6 Basic Transistor Design                                                            | 200 |

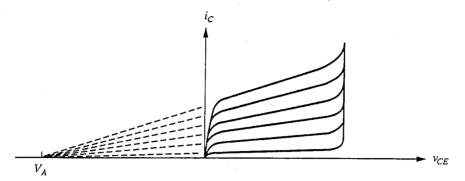

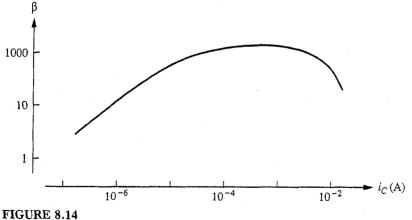

|    | 8.1.7 Beyond Ebers–Moll: Limitations of the Model                                        | 203 |

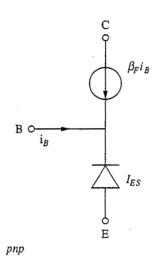

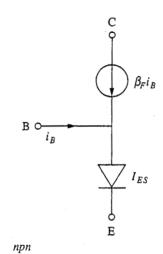

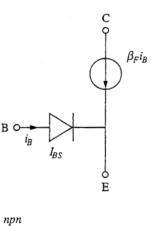

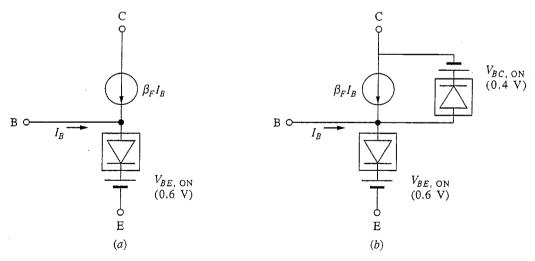

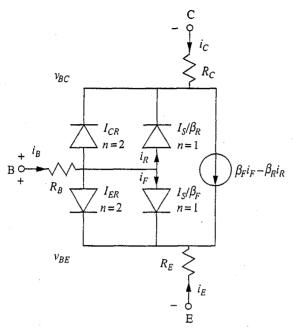

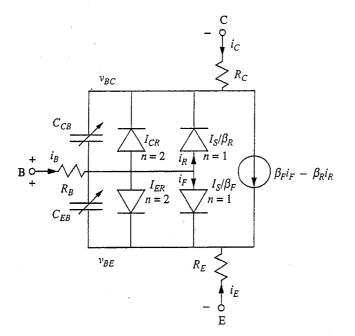

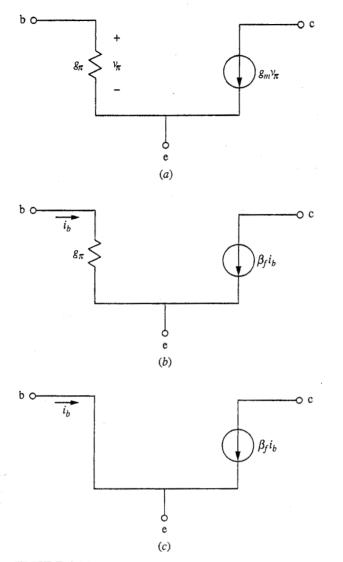

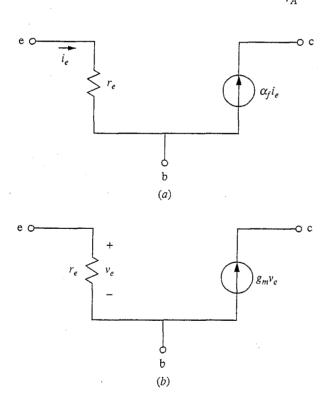

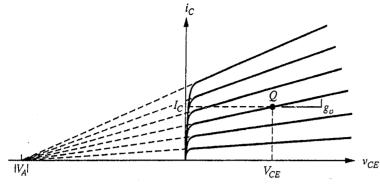

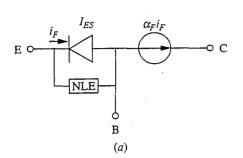

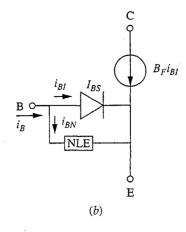

|    | 8.2 Circuit Models for Bipolar Junction Transistors                                      | 208 |

|    | 8.2.1 Large-Signal Models                                                                | 208 |

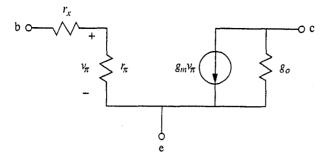

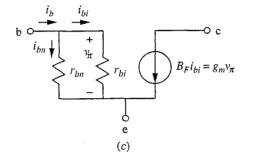

|    | 8.2.2 Static Small-Signal Linear Models                                                  | 218 |

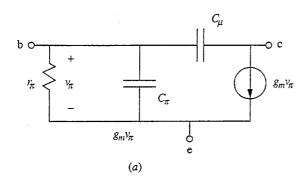

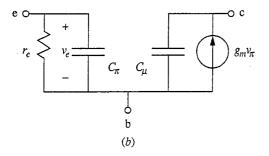

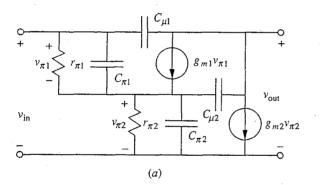

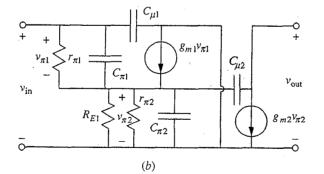

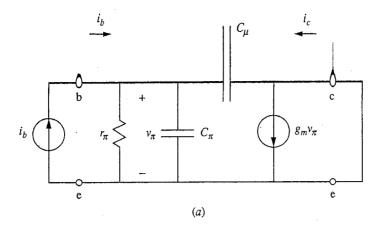

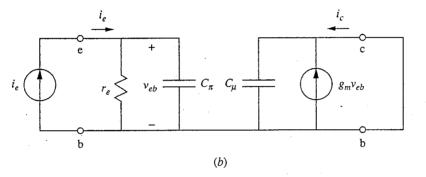

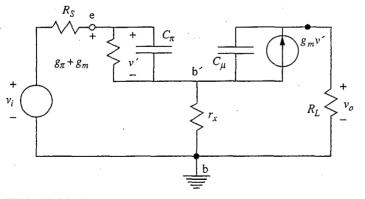

|    | 8.2.3 Dynamic Small-Signal Transistor Models                                             | 224 |

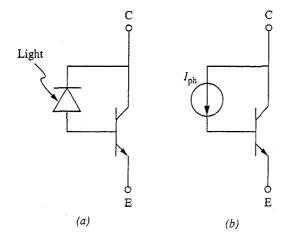

|    | 8.3 Phototransistors                                                                     | 227 |

|    | 8.4 Summary                                                                              | 231 |

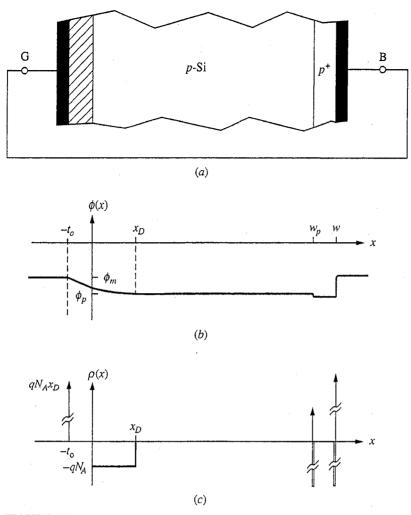

| 9  | The MOS Capacitor                                                                        | 241 |

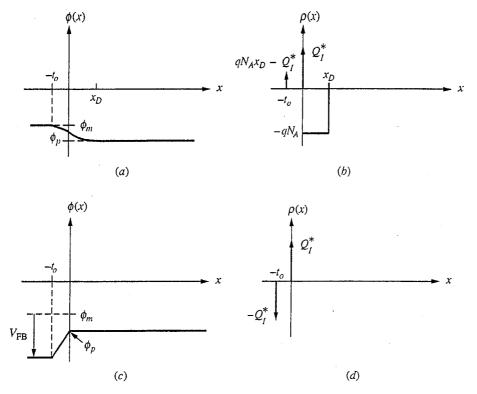

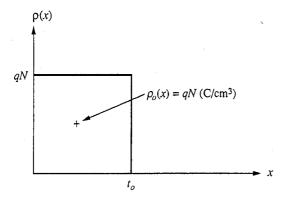

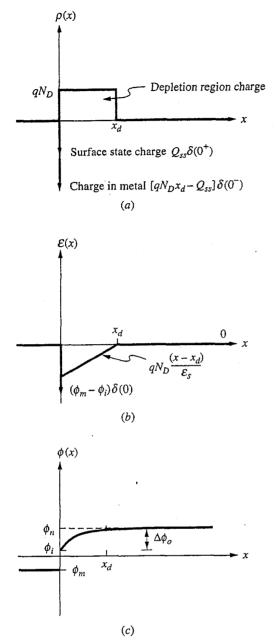

| 7  | 9.1 The MOS Capacitor in Thermal Equilibrium                                             | 241 |

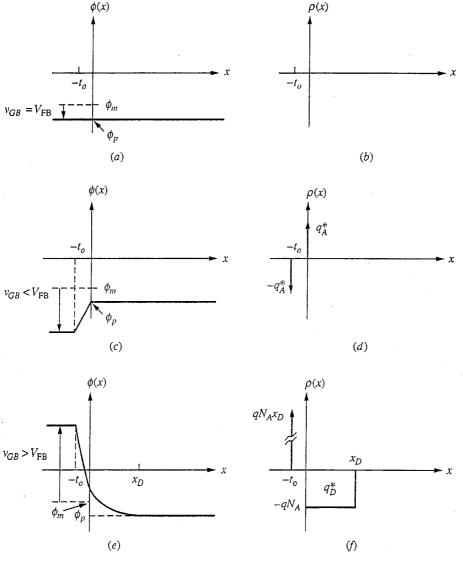

|    | 9.2 Isolated MOS Capacitor with Applied Voltage                                          | 241 |

|    | 9.2.1 Flat-band                                                                          | 243 |

|    | 9.2.2 Accumulation                                                                       | 245 |

|    | 9.2.3 Depletion                                                                          | 246 |

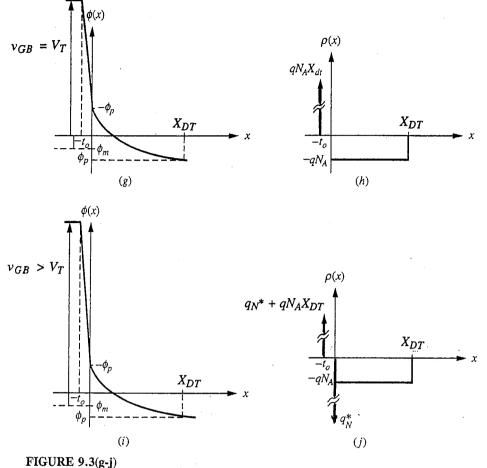

|    | 9.2.4 Threshold and Inversion                                                            | 247 |

|    | 9.3 Biased MOS Capacitor with Contact to the Channel                                     | 249 |

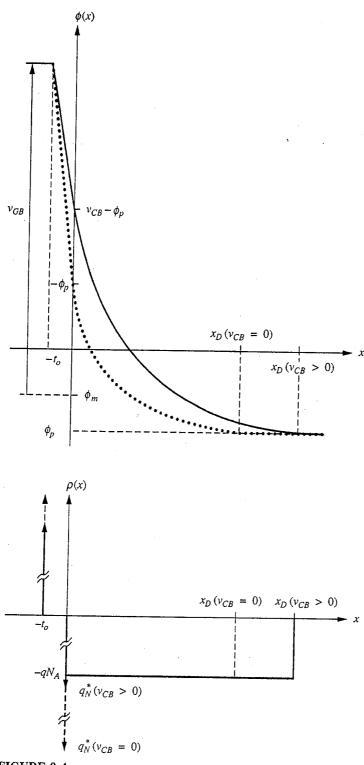

|    | 9.3.1 Direct Contact to the Channel                                                      | 249 |

|    | 9.3.2 Adjacent <i>p-n</i> Junction                                                       | 252 |

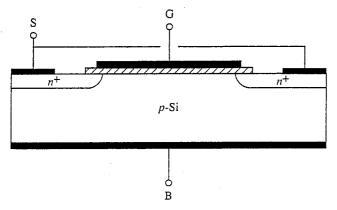

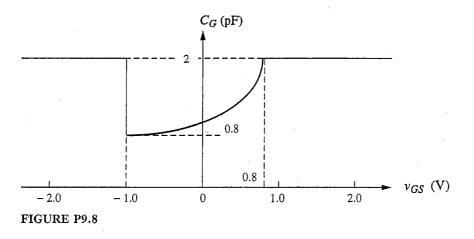

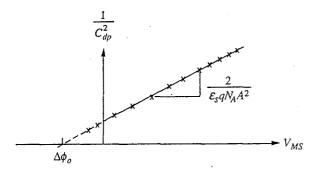

|    | 9.4 Capacitance of MOS Capacitors versus Bias                                            | 252 |

|    | 9.5 Ions and Interface Charges in MOS Structures                                         | 257 |

|    | 9.5.1 Interface Charge                                                                   | 257 |

|    | 9.5.2 Oxide Charge                                                                       | 258 |

|    | 9.6 Types of MOS Capacitors                                                              | 259 |

|    | 9.6.1 <i>n</i> -channel, <i>p</i> -type Si                                               | 260 |

|    | 9.6.2 <i>p</i> -channel, <i>n</i> -type Si                                               | 260 |

| ·  | 9.7 Summary                                                                              | 261 |

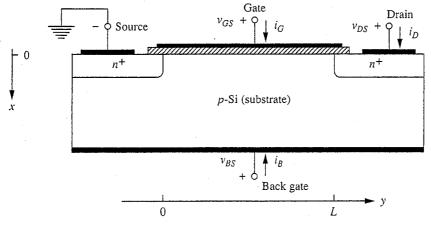

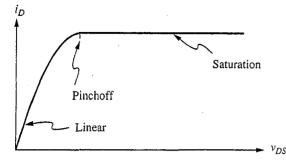

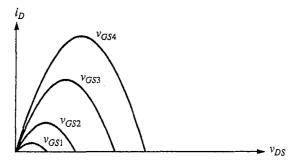

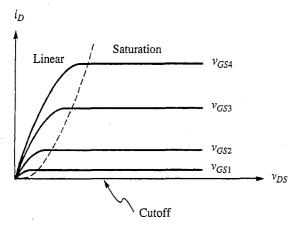

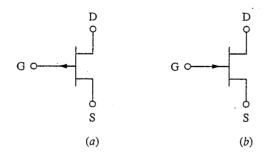

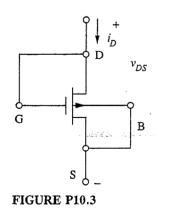

| 10 | Field Effect Transistors                                                                 | 265 |

| •  | 10.1 Metal-Oxide-Semiconductor Field Effect Transistors                                  | 266 |

|    | 10.1.1 Large-Signal Model: The Gradual Channel                                           |     |

|    | Approximation                                                                            | 268 |

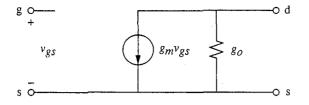

|    | 10.1.2 Static Small-Signal Linear Model                                                  | 287 |

vi contents

|    | 10.2 Junction Field Effect Transistors                        | 296 |

|----|---------------------------------------------------------------|-----|

|    | 10.2.1 Large-Signal Model                                     | 297 |

|    | 10.2.2 Static Small-Signal Linear Model                       | 303 |

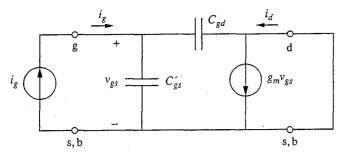

|    | 10.2.3 High-Frequency Small-Signal Model                      | 305 |

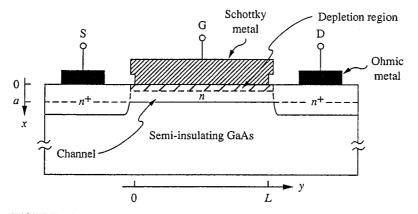

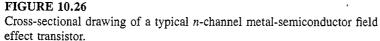

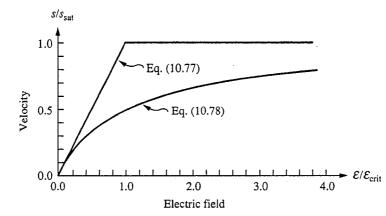

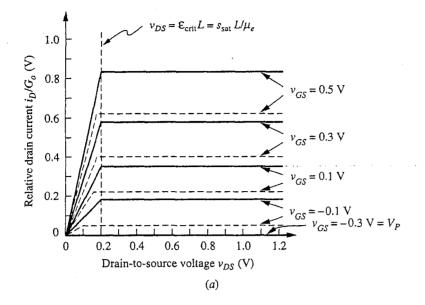

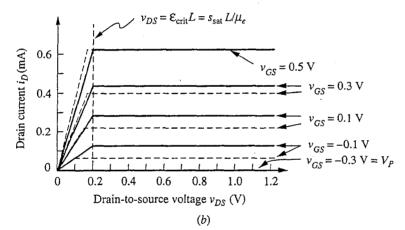

|    | 10.3 Metal-Semiconductor Field Effect Transistors             | 305 |

|    | 10.3.1 Basic Concept and Modeling                             | 305 |

|    | 10.3.2 Velocity Saturation in MESFETs                         | 307 |

|    | 10.4 Summary                                                  | 313 |

| 11 | Single-Transistor Linear Amplifier Stages                     | 317 |

|    | 11.1 Biasing Transistors                                      | 318 |

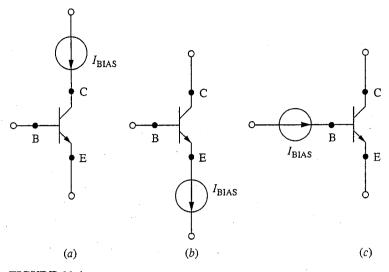

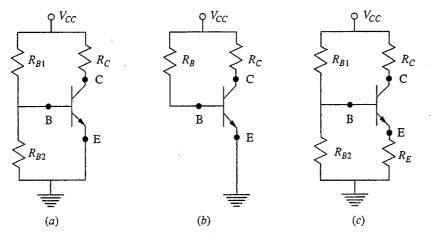

|    | 11.1.1 Bipolar Transistor Biasing                             | 318 |

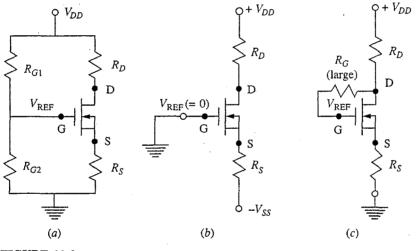

|    | 11.1.2 Field-Effect Transistor Biasing                        | 322 |

|    | 11.2 The Concept of Mid-band                                  | 325 |

|    | 11.3 Single-Bipolar-Transistor Amplifiers                     | 327 |

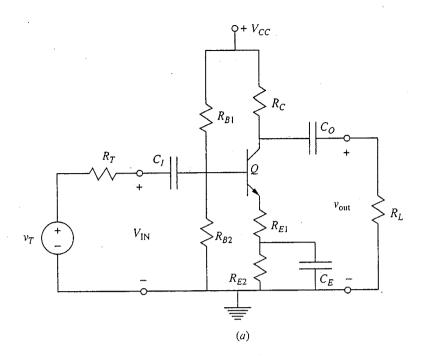

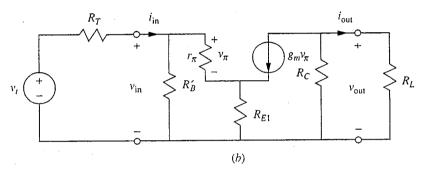

|    | 11.3.1 Common-Emitter Stage                                   | 329 |

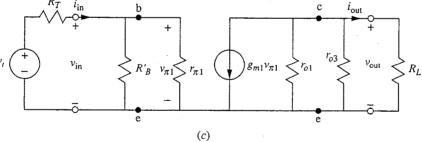

|    | 11.3.2 Degenerate-Emitter Stage                               | 338 |

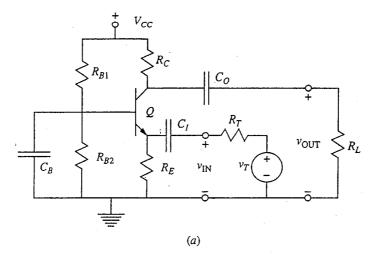

|    | 11.3.3 Common-Base Stage                                      | 341 |

|    | 11.3.4 Emitter-Follower Stage                                 | 343 |

|    | 11.4 Single Field Effect Transistor Amplifiers                | 345 |

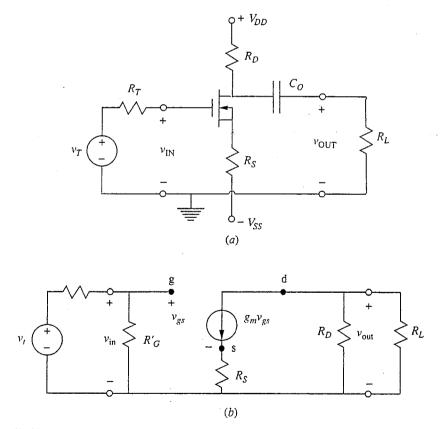

|    | 11.4.1 Common-Source Stage                                    | 346 |

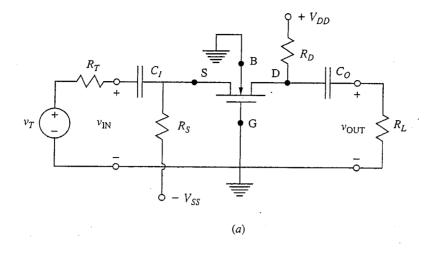

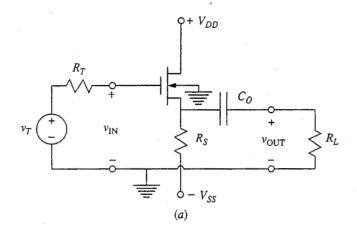

|    | 11.4.2 Degenerate-source                                      | 360 |

|    | 11.4.3 Common-gate                                            | 361 |

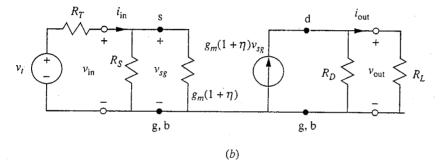

|    | 11.4.4 Source-follower                                        | 362 |

|    | 11.5 Summary                                                  | 363 |

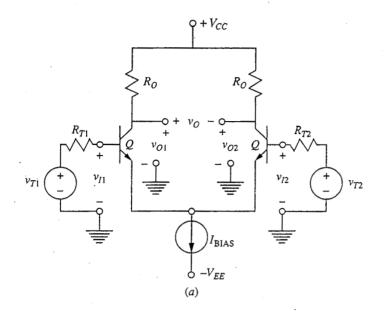

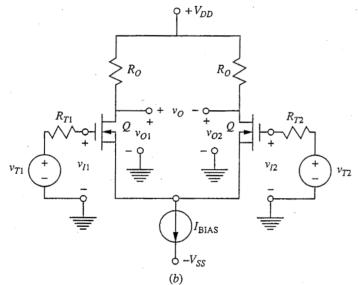

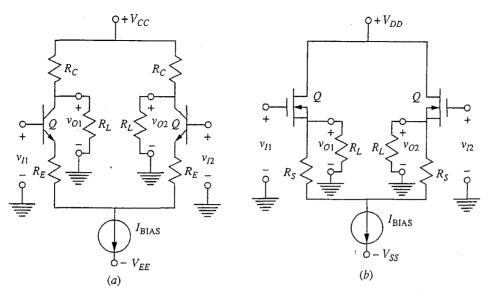

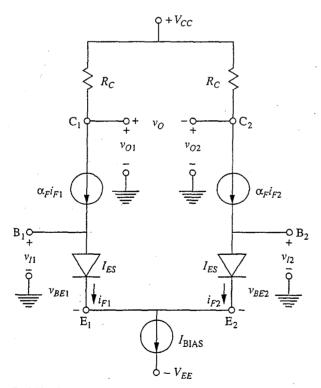

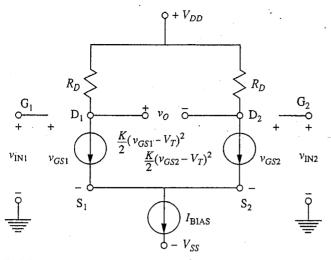

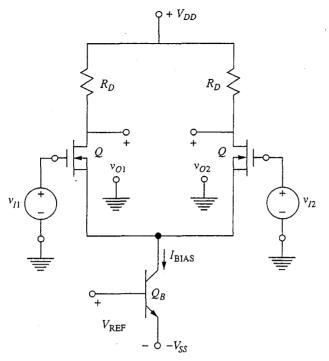

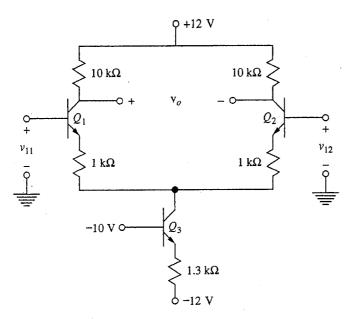

| 12 | Differential Amplifier Stages                                 | 373 |

|    | 12.1 Basic Topology                                           | 373 |

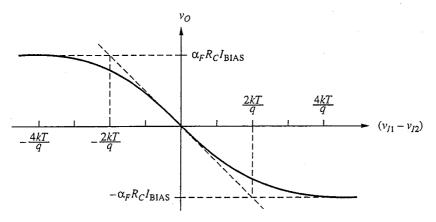

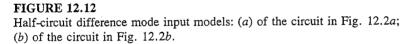

|    | 12.2 Large-Signal Analysis                                    | 375 |

|    | 12.2.1 Bipolar Differential Amplifier Transfer Characteristic | 376 |

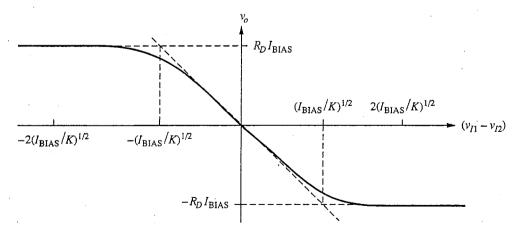

|    | 12.2.2 MOSFET Differential Amplifier Transfer Characteristic  | 378 |

|    | 12.2.3 Difference and Common Mode Inputs                      | 381 |

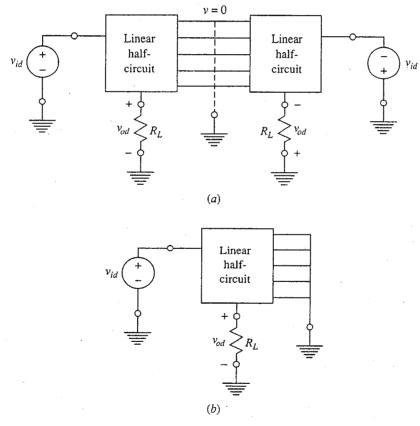

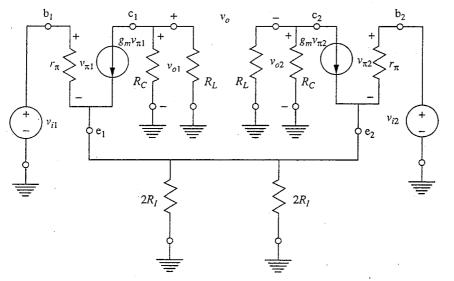

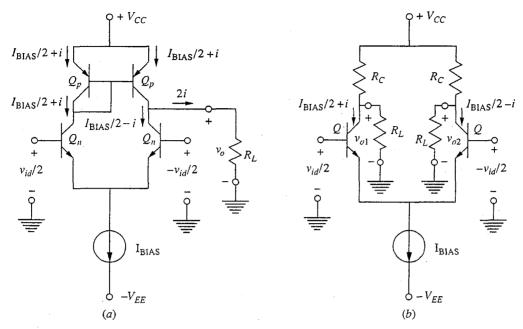

|    | 12.3 Small-Signal Linear Analysis                             | 382 |

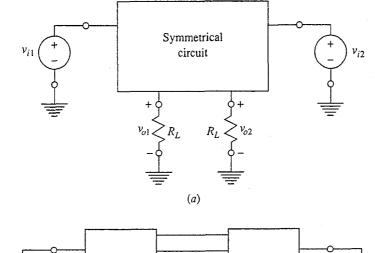

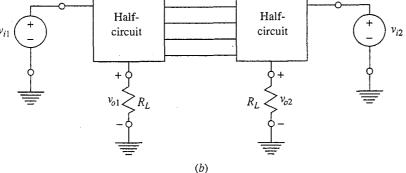

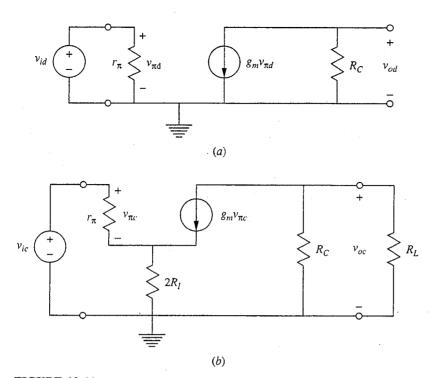

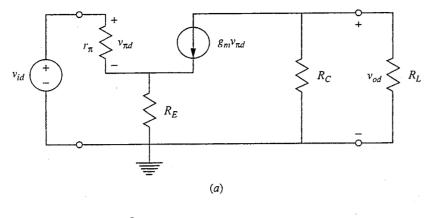

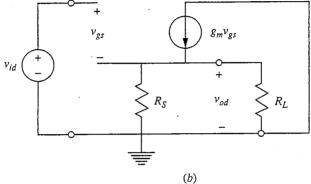

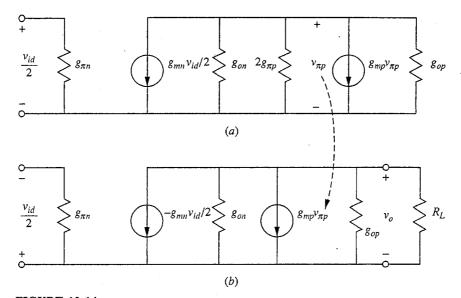

|    | 12.3.1 Half-Circuit Techniques                                | 382 |

|    | 12.3.2 Difference and Common Mode Voltage Gains               | 387 |

|    | 12.3.3 Current Gains                                          | 390 |

|    | 12.3.4 Input and Output Resistances                           | 391 |

|    | 12.4 Outputs, Current Mirrors, and Active Loads               | 392 |

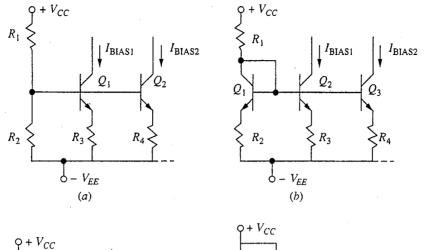

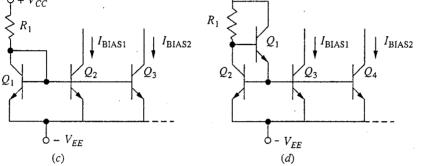

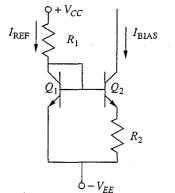

|    | 12.5 Current Source Designs                                   | 395 |

|    | 12.5.1 Bipolar Current Sources                                | 396 |

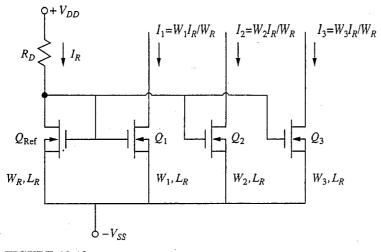

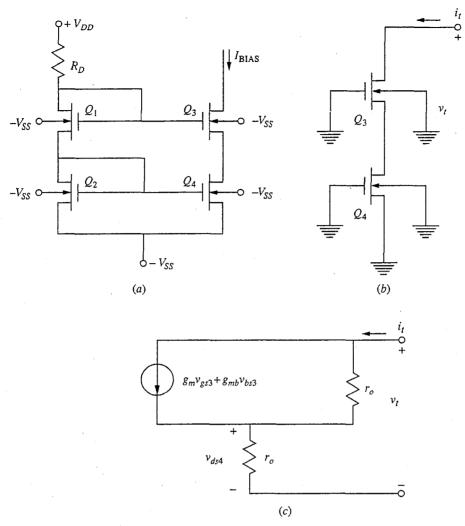

|    | 12.5.2 MOSFET Current Sources                                 | 400 |

|    | 12.6 Summary                                                  | 403 |

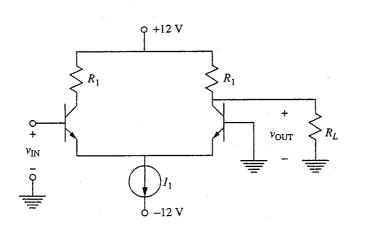

| 13 | Multistage Amplifiers                                         | 413 |

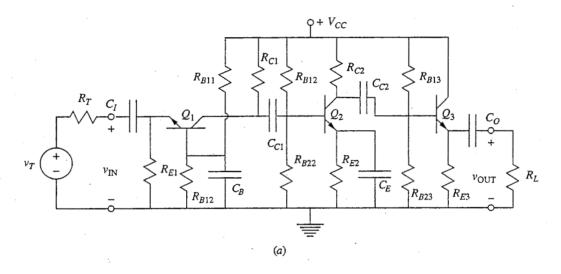

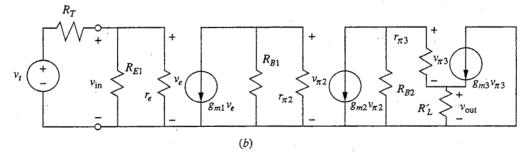

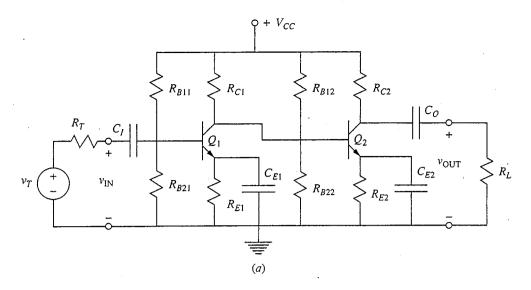

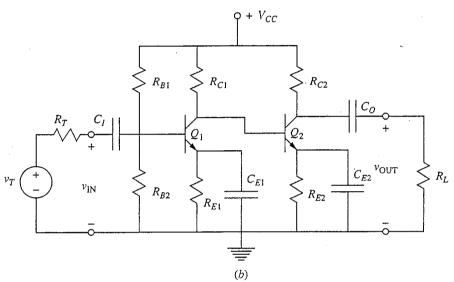

|    | 13.1 Capacitively Coupled Cascade                             | 414 |

|    | 13.2 Direct-Coupled Amplifiers                                | 419 |

|    | 13.2.1 Direct-Coupled Cascade                                 | 419 |

|    | 13.2.2 Cascode                                                | 422 |

|    | 13.2.3 Darlington                                             | 424 |

|    | 13.2.4 Emitter/Source-Coupled Cascode                         | 430 |

|    | 13.2.5 Complementary Output                                   | 433 |

|      | 13.3 Multistage Differential Amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 437                                                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

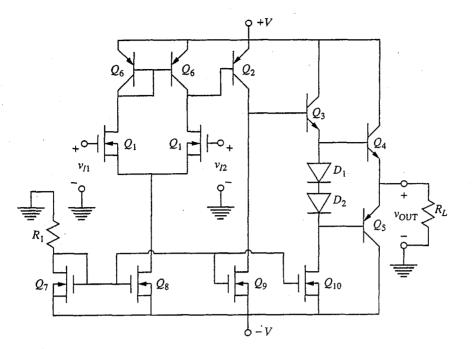

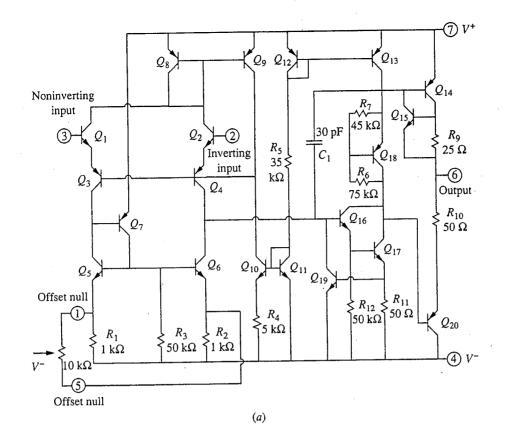

|      | 13.4 A Design Exercise: A Basic npn Op-Amp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 443                                                                                                                                                    |

|      | 13.4.1 The Parts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 443                                                                                                                                                    |

|      | 13.4.2 The Whole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 447                                                                                                                                                    |

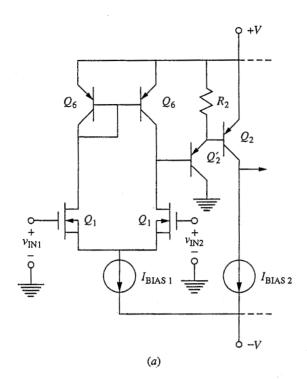

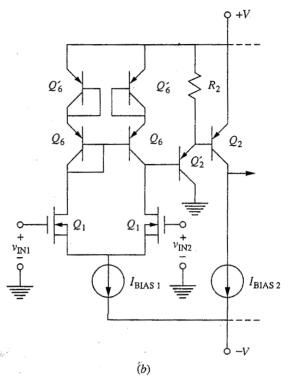

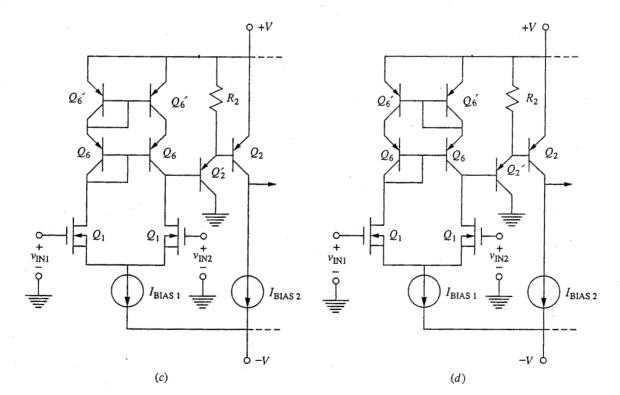

|      | 13.5 Beyond Basic: Design with BiCMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 449                                                                                                                                                    |

|      | 13.5.1 Darlington Second Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 452                                                                                                                                                    |

|      | 13.5.2 p-MOS Current Mirror and Second Stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 454                                                                                                                                                    |

|      | 13.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 457                                                                                                                                                    |

| 14   | High-Frequency Analysis of Linear Amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 465                                                                                                                                                    |

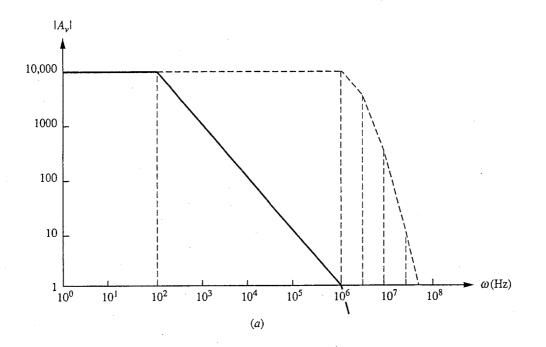

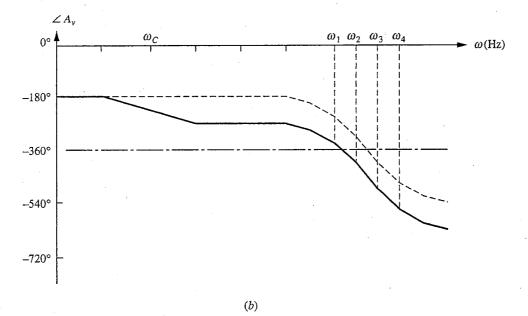

|      | 14.1 Determining the Bounds of the Mid-Band Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 465                                                                                                                                                    |

|      | 14.1.1 Method of Open-Circuit Time Constants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 466                                                                                                                                                    |

|      | 14.1.2 Method of Short-Circuit Time Constants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 467                                                                                                                                                    |

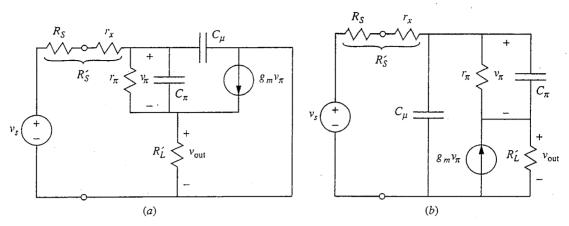

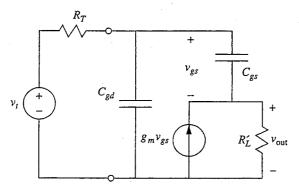

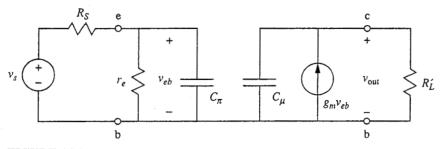

|      | 14.2 Examination of Specific Circuit Topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 468                                                                                                                                                    |

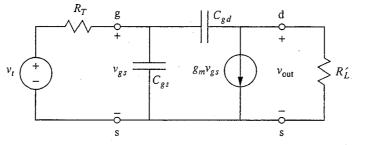

|      | 14.2.1 Common-Emitter/Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 468                                                                                                                                                    |

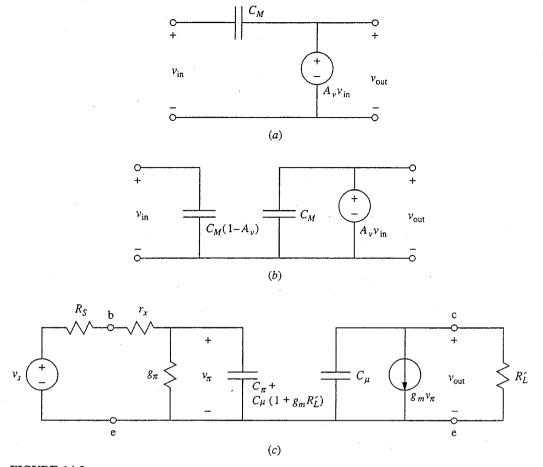

|      | 14.2.2 The Miller Effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 472                                                                                                                                                    |

|      | 14.2.3 Degenerate-Emitter/Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 476                                                                                                                                                    |

|      | 14.2.4 Emitter/Source-Follower                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 476                                                                                                                                                    |

|      | 14.2.5 Common-Base/Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 479                                                                                                                                                    |

|      | 14.2.6 Cascode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 481                                                                                                                                                    |

|      | 14.2.7 Darlington Pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 483                                                                                                                                                    |

|      | 14.3 Intrinsic High-Frequency Limits of Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 484                                                                                                                                                    |

|      | 14.3.1 Bipolar Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 484                                                                                                                                                    |

|      | 14.3.2 Field Effect Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 487                                                                                                                                                    |

|      | 14.4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 493                                                                                                                                                    |

| 15   | Digital Building-Block Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 499                                                                                                                                                    |

| TO . |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                        |

| 10   | 15.1 Generic Binary Logic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 500                                                                                                                                                    |

| 1.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                        |

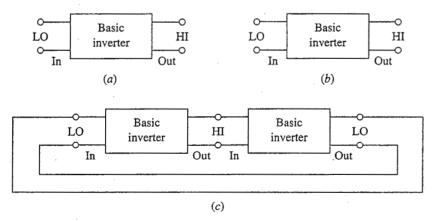

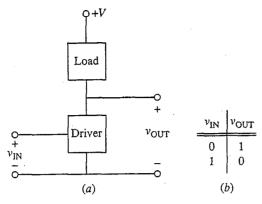

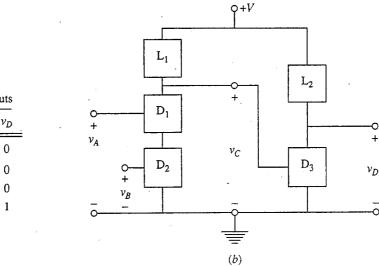

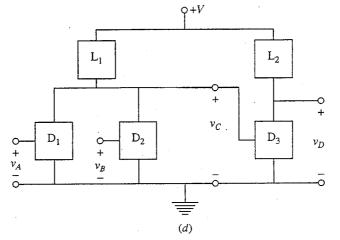

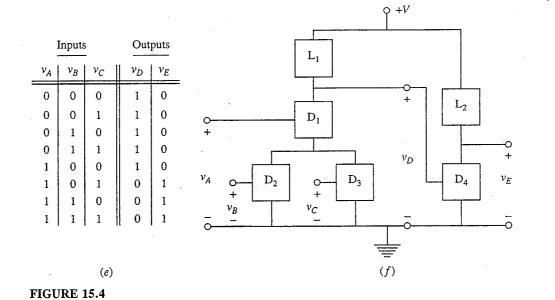

|      | <ul><li>15.1 Generic Binary Logic Circuits</li><li>15.1.1 Generic Inverter</li><li>15.1.2 Realizing Logic Functions with Inverters</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 500<br>500<br>501                                                                                                                                      |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 500<br>500<br>501<br>504                                                                                                                               |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 500<br>500<br>501<br>504<br>509                                                                                                                        |

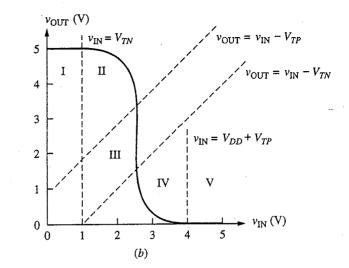

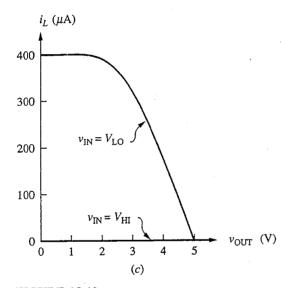

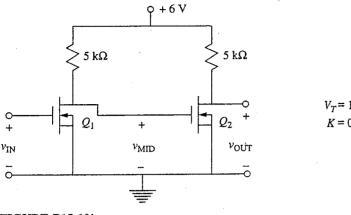

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 500<br>500<br>501<br>504<br>509<br>510                                                                                                                 |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 500<br>500<br>501<br>504<br>509<br>510<br>511                                                                                                          |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                               | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514                                                                                                   |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: n-MOS</li> </ul>                                                                                                                                                                                                                                                                                                                                                                    | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514<br>516                                                                                            |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: n-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> </ul>                                                                                                                                                                                                                                                                                                                           | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514<br>516<br>521                                                                                     |

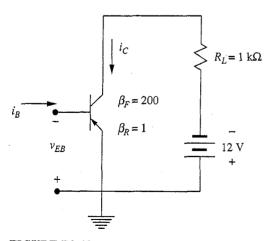

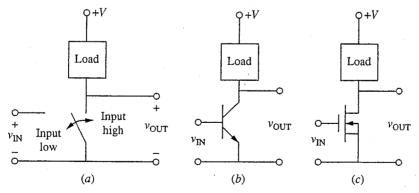

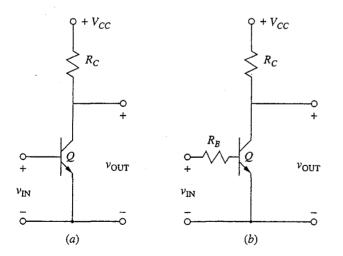

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: n-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> </ul>                                                                                                                                                                                                                                                                                           | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514<br>516<br>521<br>524                                                                              |

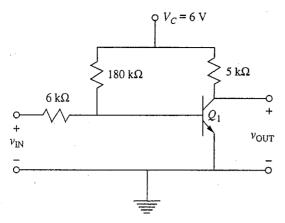

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: n-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> </ul>                                                                                                                                                                                                                                               | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514<br>516<br>521<br>524<br>525                                                                       |

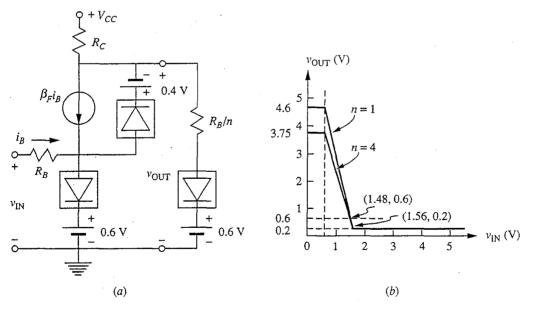

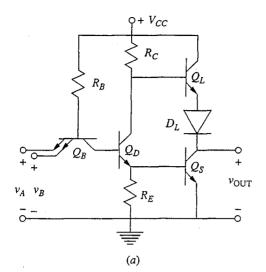

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: n-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> <li>15.3.2 Transistor-Transistor Logic: TTL</li> </ul>                                                                                                                                                                                              | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514<br>516<br>521<br>524<br>525<br>527                                                                |

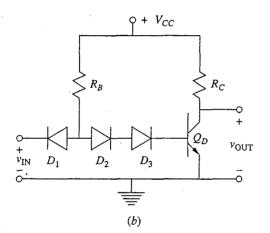

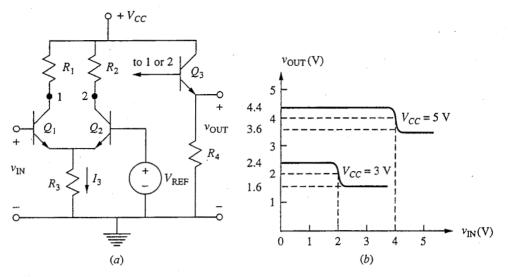

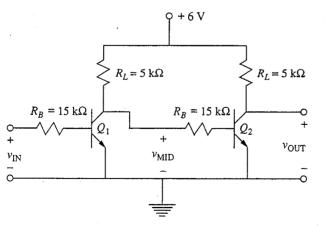

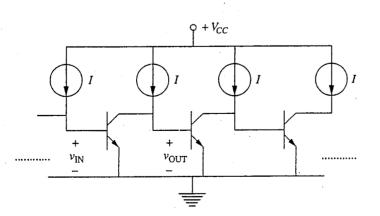

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: n-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> <li>15.3.2 Transistor-Transistor Logic: TTL</li> <li>15.3.3 Emitter-Coupled Logic: ECL</li> </ul>                                                                                                                                                   | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514<br>516<br>521<br>524<br>525<br>527<br>531                                                         |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: <i>n</i>-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> <li>15.3.2 Transistor-Transistor Logic: TTL</li> <li>15.3.3 Emitter-Coupled Logic: ECL</li> <li>15.4 Memory Cells</li> </ul>                                                                                                                 | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514<br>516<br>521<br>524<br>525<br>527<br>531<br>534                                                  |

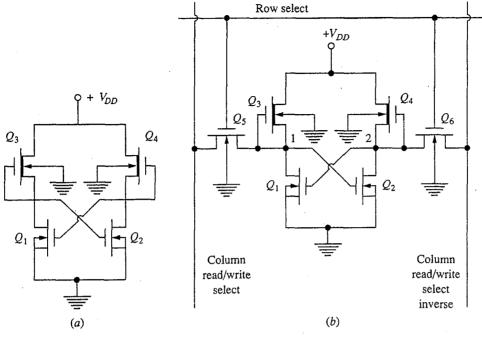

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: <i>n</i>-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> <li>15.3.2 Transistor-Transistor Logic: TTL</li> <li>15.3.3 Emitter-Coupled Logic: ECL</li> <li>15.4 Memory Cells</li> <li>15.4.1 Static Memory Cells</li> </ul>                                                                             | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514<br>516<br>521<br>524<br>525<br>527<br>531<br>534<br>535                                           |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: <i>n</i>-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> <li>15.3.2 Transistor-Transistor Logic: TTL</li> <li>15.3.3 Emitter-Coupled Logic: ECL</li> <li>15.4 Memory Cells</li> </ul>                                                                                                                 | 500<br>500<br>501<br>504<br>509<br>510<br>511<br>514<br>516<br>521<br>524<br>525<br>527<br>531<br>534                                                  |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: <i>n</i>-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> <li>15.3.2 Transistor-Transistor Logic: TTL</li> <li>15.3.3 Emitter-Coupled Logic: ECL</li> <li>15.4 Memory Cells</li> <li>15.4.1 Static Memory Cells</li> <li>15.5 Summary</li> </ul>                                                       | $\begin{array}{c} 500\\ 500\\ 501\\ 504\\ 509\\ 510\\ 511\\ 514\\ 516\\ 521\\ 524\\ 525\\ 527\\ 531\\ 534\\ 535\\ 538\\ 540\\ \end{array}$             |

| 16   | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: <i>n</i>-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> <li>15.3.2 Transistor-Transistor Logic: TTL</li> <li>15.3.3 Emitter-Coupled Logic: ECL</li> <li>15.4 Memory Cells</li> <li>15.4.1 Static Memory Cells</li> <li>15.5 Summary</li> <li>Switching Transients in Devices and Circuits</li> </ul> | $\begin{array}{c} 500\\ 500\\ 501\\ 504\\ 509\\ 510\\ 511\\ 514\\ 516\\ 521\\ 524\\ 525\\ 527\\ 531\\ 534\\ 535\\ 538\\ 540\\ 547\\ \end{array}$       |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: <i>n</i>-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> <li>15.3.2 Transistor-Transistor Logic: TTL</li> <li>15.3 Emitter-Coupled Logic: ECL</li> <li>15.4 Memory Cells</li> <li>15.4.1 Static Memory Cells</li> <li>15.5 Summary</li> </ul> Switching Transients in Devices and Circuits            | $\begin{array}{c} 500\\ 500\\ 501\\ 504\\ 509\\ 510\\ 511\\ 514\\ 516\\ 521\\ 524\\ 525\\ 527\\ 531\\ 534\\ 535\\ 538\\ 540\\ 547\\ 548\\ \end{array}$ |

|      | <ul> <li>15.1 Generic Binary Logic Circuits</li> <li>15.1.1 Generic Inverter</li> <li>15.1.2 Realizing Logic Functions with Inverters</li> <li>15.1.3 Objectives in Inverter Design</li> <li>15.1.4 Determining the Transfer Characteristic</li> <li>15.2 MOSFET Logic</li> <li>15.2.1 Resistor Load</li> <li>15.2.2 Enhancement Mode Loads</li> <li>15.2.3 Depletion Mode Load: <i>n</i>-MOS</li> <li>15.2.4 Complementary Load: CMOS</li> <li>15.3 Bipolar Inverters</li> <li>15.3.1 The Simple Bipolar Inverter</li> <li>15.3.2 Transistor-Transistor Logic: TTL</li> <li>15.3.3 Emitter-Coupled Logic: ECL</li> <li>15.4 Memory Cells</li> <li>15.4.1 Static Memory Cells</li> <li>15.5 Summary</li> <li>Switching Transients in Devices and Circuits</li> </ul> | $\begin{array}{c} 500\\ 500\\ 501\\ 504\\ 509\\ 510\\ 511\\ 514\\ 516\\ 521\\ 524\\ 525\\ 527\\ 531\\ 534\\ 535\\ 538\\ 540\\ 547\\ \end{array}$       |

|   | 16.3 In   | verter Switching Times and Gate Delays                | 572     |

|---|-----------|-------------------------------------------------------|---------|

|   | 16.3.1    | CMOS and Other MOSFET Inverters                       | 572     |

|   | 16.3.2    | TTL and ECL Gates                                     | 577     |

|   | 16.3.3    | Device and Circuit Scaling                            | 580     |

|   | 16.4 Su   | immary                                                | 585     |

| A | ppendix   | es                                                    |         |

| Α |           | epresentative Properties of Common Semiconductors     | 591     |

| В |           | Holes and Electrons                                   | 593     |

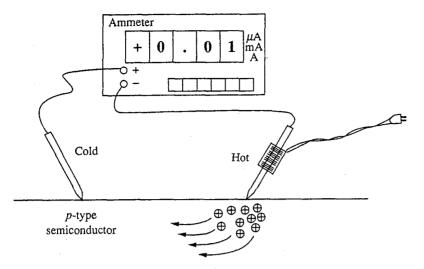

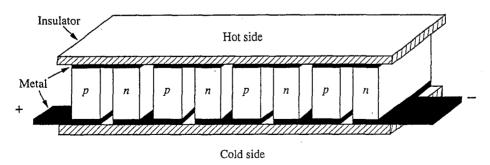

|   | Ų         | t Point Probe Measurement                             | 593     |

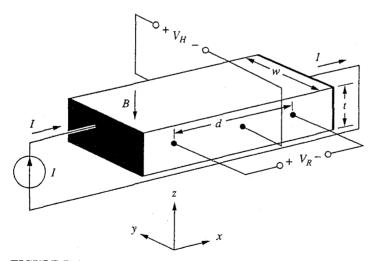

|   | B.2 Ha    | ll Effect Measurement                                 | 595     |

| С | Some In   | nportant Concepts of Solid-State Physics              | 599     |

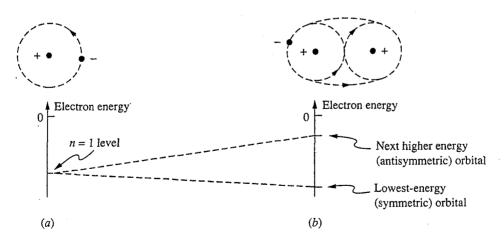

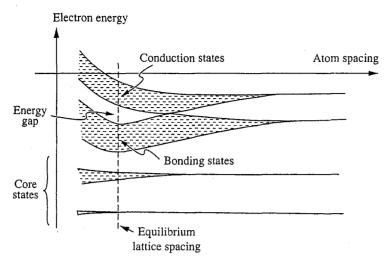

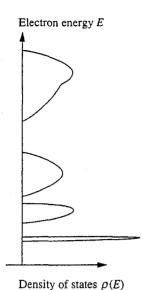

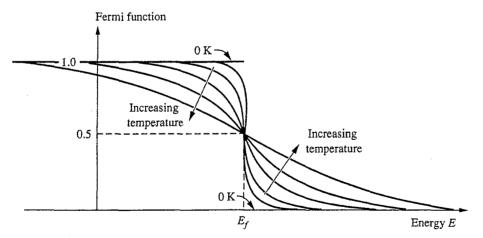

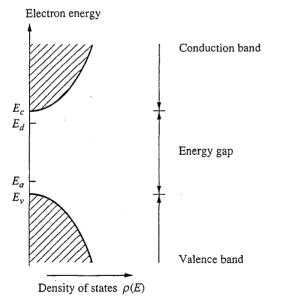

|   |           | ergy Bands                                            | 599     |

|   | C.2 Eff   | ective Mass Theory                                    | 612     |

| D | Quantify  | ving the Tendency to Quasineutrality                  | 615     |

|   | D.1 Un    | iform Time-varying Excitation: $\tau_D$               | 616     |

|   | D.2 No    | n-uniform Static Excitation: L <sub>De</sub>          | 617     |

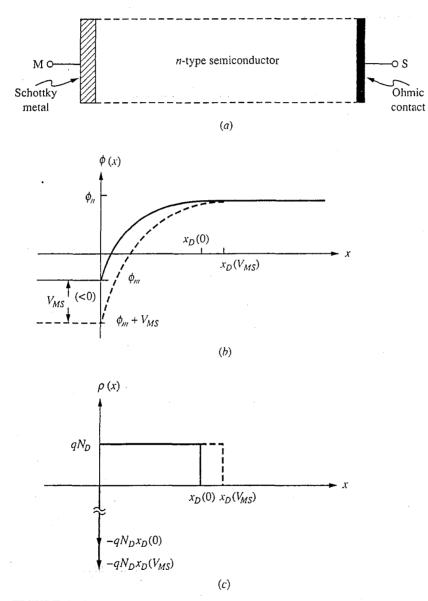

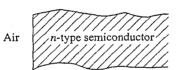

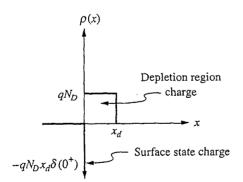

| E |           | emiconductor Contacts and Devices                     | 619     |

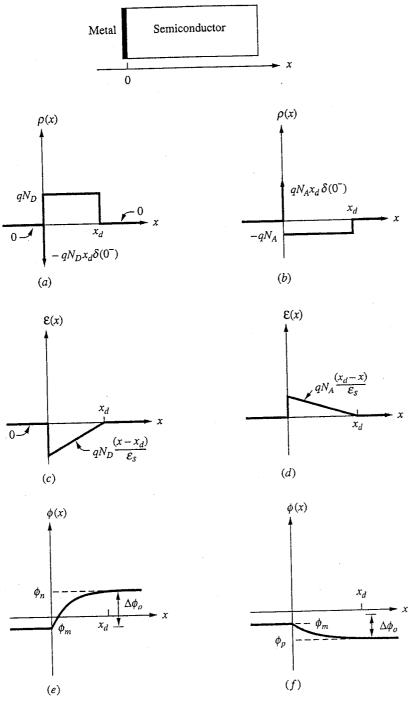

|   | E.1 The   | e Metal-Semiconductor Junction in Thermal Equilibrium | 619     |

|   | E.2 Rev   | verse Biased Metal-Semiconductor Junctions            | 625     |

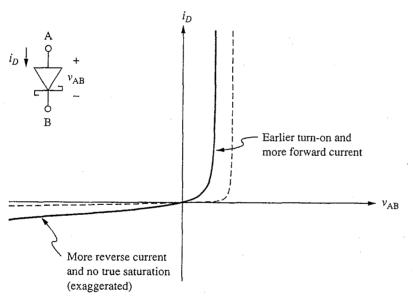

|   | E.3 For   | ward Bias and Currents                                | 625     |

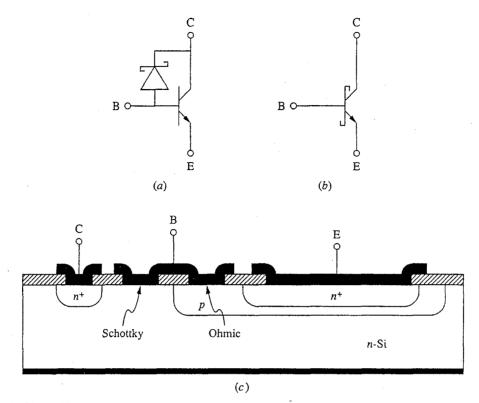

|   | E.4 Sch   | ottky Diodes                                          | 628     |

|   | E.5 Oh    | mic Contacts                                          | 630     |

| F | Large- a  | nd Small-signal Values of $\beta$                     | 631     |

| G | Integrate | ed Circuit Fabrication                                | 637     |

|   | G.1 Eler  | ments of Semiconductor Processing                     | 637     |

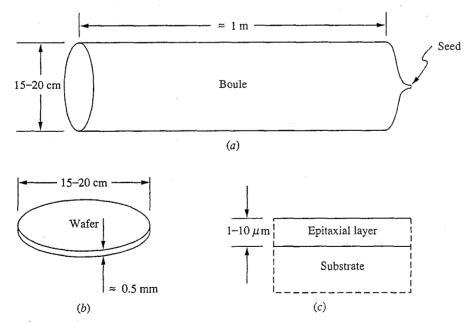

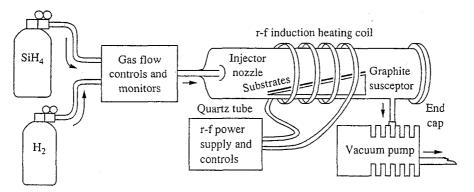

|   | G.1.1     | Crystal Growth                                        | 638     |

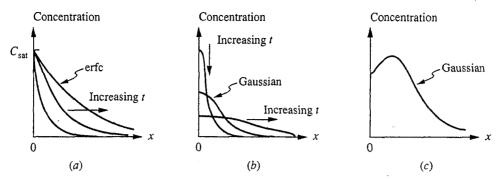

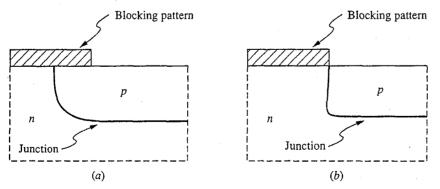

|   | G.1.2     | Doping                                                | 640     |

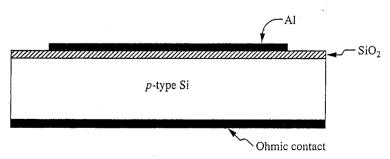

|   | G.1.3     | Encapsulation                                         | 642     |

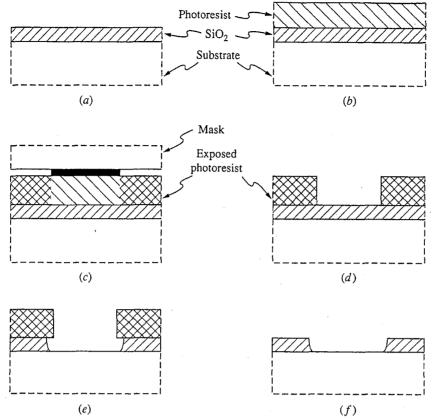

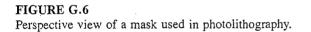

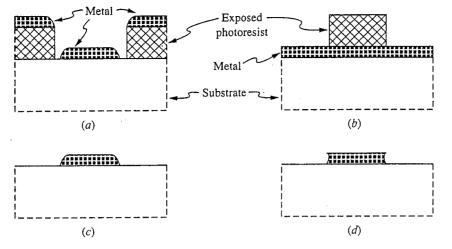

|   |           | Microlithography                                      | 644     |

|   | G.1.5     | Metallization                                         | 647     |

|   | G.1.6     | Etching and Cleaning                                  | 648     |

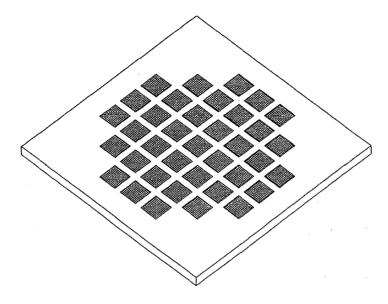

|   | G.2 Exa   | mples of Integrated Circuit Processes                 | 649     |

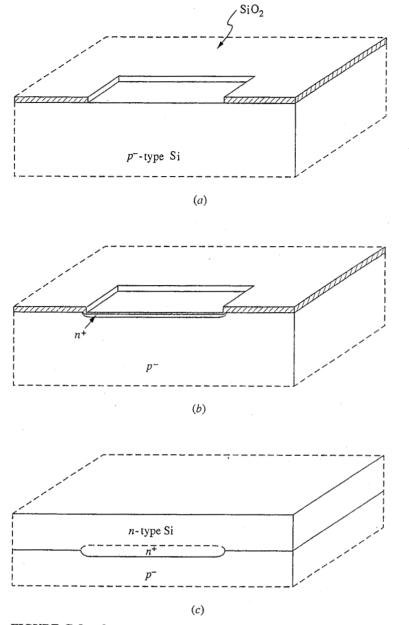

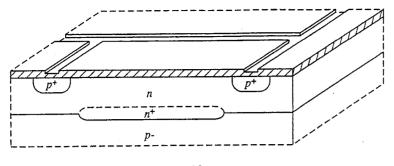

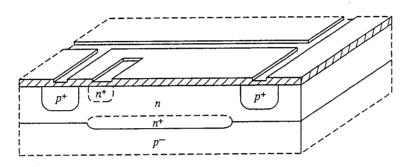

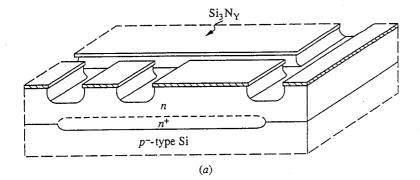

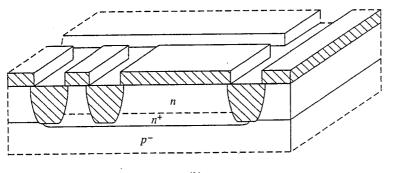

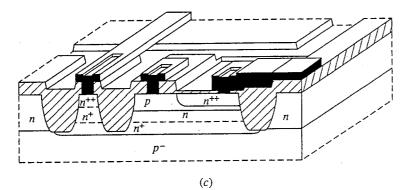

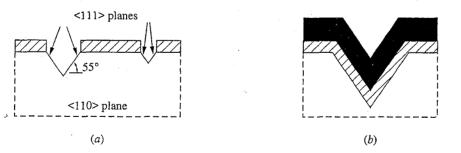

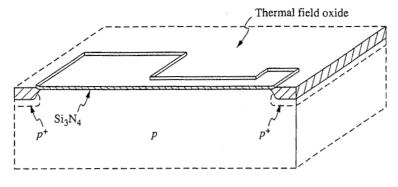

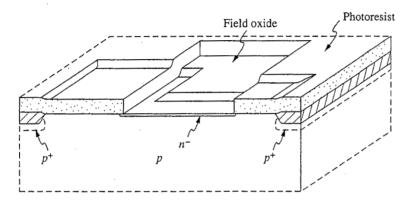

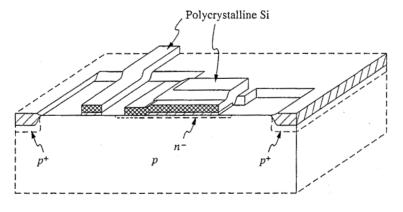

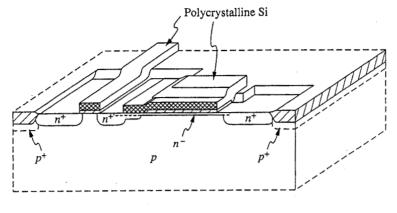

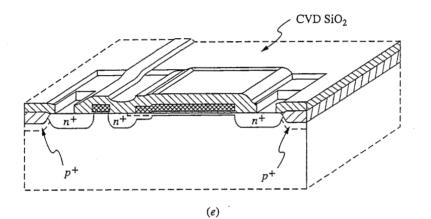

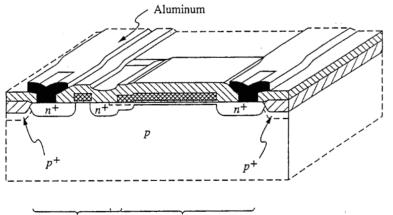

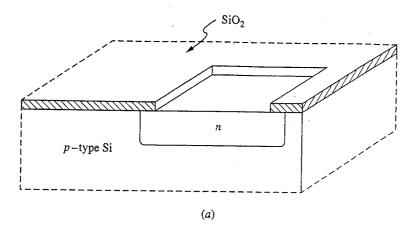

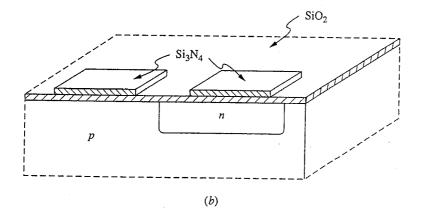

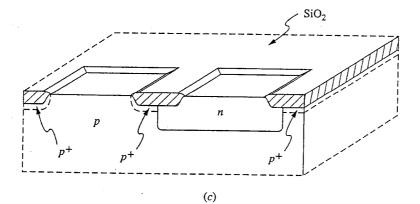

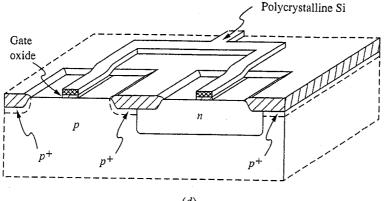

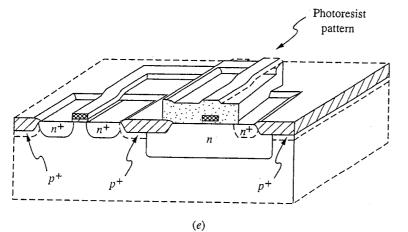

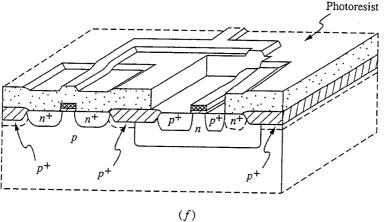

|   | G.2.1     |                                                       | 650     |

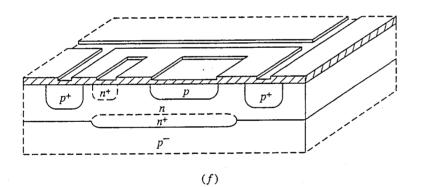

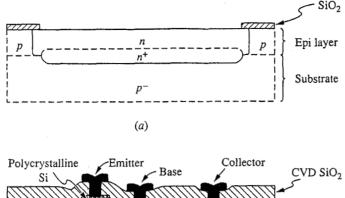

|   | G.2.2     |                                                       | 656     |

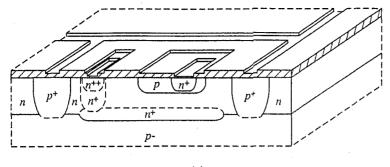

|   | G.2.3     | -                                                     | 660     |

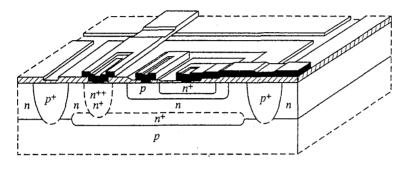

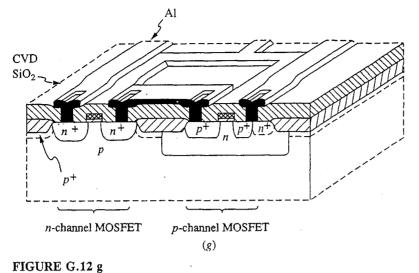

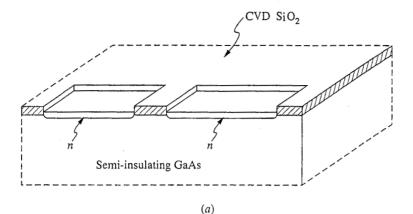

|   |           | A Silicon-Gate CMOS Process                           | 664     |

|   | G.2.5     |                                                       | 668     |

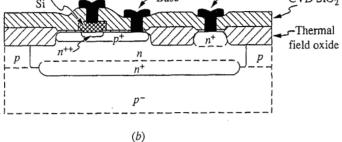

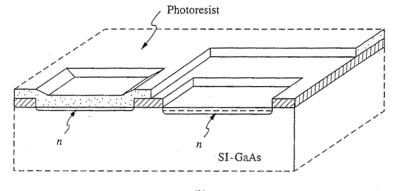

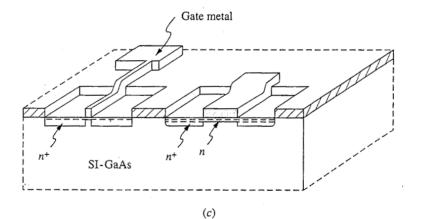

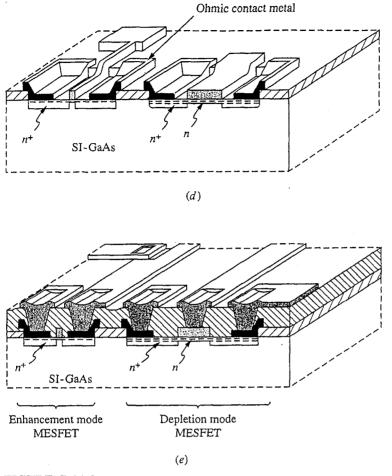

|   | G.2.6     | GaAs Enhancement/Depletion Mode                       |         |

|   |           | Digital Logic Process                                 | 670     |

| т | 1         |                                                       | <i></i> |

Index

675

# PREFACE

Most books exist because the authors felt that there were no other books that said what they felt needed to be said in the way they wanted to say it. I felt that a different book was needed, too, and this book is my attempt to fill that need. This text is "different" for what it does not include as well as for what it does include, and this uniqueness merits some discussion.

First, this text *does* span a range of topics from semiconductor physics to device function and modeling to circuit analysis and design. It is a basic premise of this text that it is important in a first course on semiconductor electronics to address this broad range of topics. Only in this way can we adequately emphasize from the beginning the interactions between physics, devices, and circuits in modern integrated system design.

Second, this text *does not* include, except as an appendix, semiconductor band theory or any of the associated theoretical baggage that implies (e.g., Fermi statistics, effective mass theory, etc.). It is another basic premise of this text that such material is best left for later, specialized courses and is in fact not necessary for a first, thorough treatment; you do not need to understand energy bands to understand p-n junctions, bipolar transistors, and FETs. As a consequence this text can be used by college sophomores who have had only a basic introduction to physics and circuits. More importantly, by teaching no more semiconductor physics than is necessary to understand the devices, this text can place more emphasis on actually developing this understanding.

Third, this text *does* take as its mission to teach the broader topic of modeling using semiconductor electronics as a vehicle. Therefore it is a text that should be of value to all engineering students. If you learn something about semiconductor electronics, so much the better, but you will certainly gain an appreciation of the issues inherent in developing and applying physical models.

At the same time, this text *does not* emphasize the use of sophisticated computer models. The focus here is instead on understanding and choosing between various approximate models to select one that might be suitable, for example, for a back-of-the-envelope calculation, estimation, and/or evaluation of a design concept. Computer models have their place and are extremely important for engineers, but in a text at this level they are more dangerous than anything else since they tend to work against developing the insight we seek.

ix

Fifth, this text *does* include design, as well as analysis. Design is admittedly not a main focus, nor is much time devoted specifically to it, but some design excercises are included, and a design experience is recommended as a complement to any course based on this text. Only through the exercise of design—of, for example, choosing a circuit topology and, given a topology, selecting component values to achieve certain performance goals—can the lessons of this text be truly learned.

Sixth, this text *does not* attempt to be the final word on any of the topics it addresses. It presents a correct first treatment and imparts a functional level of knowledge, but it is also only preparation for a second tier of specialization, be it in physics, devices, circuits, and/or systems, that surely must follow.

Seventh, this text *does* contain much more material than can be covered in any one course; yet, eighth, an instructor using this text *does not* have to use all of this material, nor, in fact, does he or she have to use it in the order it appears in the table of contents. I have attempted to write this text in such a way that it is possible to use many different subsets and orderings of the material, and in such a way that discussions of more advanced modeling and of more specialized and less pervasive devices can be skipped over without loss of continuity. (Please see "Comments on Using This Text" below for more on these points.)

Also, this text does have its roots in a long legacy of semiconductor electronics education at MIT, and none of the preceding litany of do's and don'ts are claimed to be original to this text. In 1960 the Semiconductor Electronics Education Committee (SEEC) was formed under the leadership of MIT faculty members to address the question of undergraduate electrical engineering education in light of the dramatic changes that were then taking place in the field of electronics with the advent of the silicon transistor and integrated-circuit technology. An important product of that effort was an appreciation for the close coupling between semiconductor physics, device modeling, and circuit analysis and for the value of teaching these topics in a coherent unit. The SEEC produced an excellent, very carefully written series of seven paperback volumes and led indirectly to the publication of a textbook: Electronic Principles-Physics, Models, and Circuits by Paul E. Gray and Campbell L. Searle (Wiley, New York, 1969). The present text unashamedly builds upon these SEEC foundations. It addresses a similarly broad range of topics at a similarly accessible level, differing primarily only in that it does so in a way that reflects the field of semiconductor electronics as it exists now over 30 years after SEEC (i.e., in the 1990s).

# COMMENTS ON USING THIS TEXT

As stated earlier, I have attempted to write this text in such a way that it is possible to use many different subsets and orderings of the material, and I have used it to teach the subject 6.012—Electronic Devices and Circuits at MIT following several topic sequences. The order in which the material appears in this text is a relatively traditional one and it works well. It does, however, mean that circuits are discussed only after a considerable amount of time has been spent on physics and devices. A convenient, timely way to get circuits in sooner is to present the MOSFET before the BJT, and to discuss MOS logic circuits right after finishing the MOSFET. When doing this, I have found that it is useful to follow the text through the reverse biased p-n diode (Section 7.2) so the depletion approximation has been introduced, and to then go to Chapters 9, 10, and 15 before returning to Chapter 7 and continuing with Section 7.3.

Chapters 14 and 16 contain material that can also be presented earlier with good effect. One can easily argue that all of the material in these chapters could have been integrated into the earlier device and circuits chapters, but I resisted doing this because I feel it is useful to have the discussions of frequency response collected in one place; the same is true of the switching transients discussions. Having said this, however, I do usually include the discussion of switching times of MOSFET inverters with the discussion of their other characteristics. Another example is the switching transient of a p-n diode, which is a good issue to discuss soon after teaching diode current flow. The fact that there are plenty of carriers to sustain a reverse current immediately after a diode has been switched from forward to reverse bias is easy to see, and it reinforces the students' understanding of current flow in a diode.

Finally, it is important to realize that we are unable to cover all of the material in this text in our one-semester course at MIT. Typically, we wait until a senior-level device elective to cover the more advanced device models: to discuss JFETs and MESFETs, optoelectronic devices, memory, and bipolar logic; and to cover much of the discussion of large signal switching transients. I recommend considering the following topics and sections (section numbers in parentheses) when you are looking for material to delete or de-emphasize: physics issues such as high-level injection solutions (3.2.3) and certain boundary conditions (5.2.3)c-e); advanced models for diodes (7.4.1b), BJTs (8.2.1b), and MOSFETs (10.1.1b); and certain more specialized or less pervasive devices such as photoconductors (3.3), photodiodes (7.5), LEDs (7.6), phototransistors (8.3), JFETs (10.2), MESFETs (10.3), memory cells (15.4), and charge-coupled devices (16.2.2b). If, on the other hand, you are looking to expand upon, or add to, any of the material in the main text, there is ample material in the appendices presented at much the same level on energy bands, Fermi statistics, and the effective mass picture (Appendix C), on metal-semiconductor junctions (Appendix E), and on processing (Appendix G).

#### ACKNOWLEDGMENTS

First and foremost, I thank my wife, Carmenza, and my sons, Nils and Diego, for their support, tolerance, and love throughout this project.

The present text reflects very much the philosophy of the late Professor Richard B. Adler, who had a great influence on me since the day I first set foot on the MIT campus. Many others, including Professors A. C. Smith, R. F. Morgenthaler, D. J. Epstein, and R. H. Kyhl, have also taught me a great deal about this material and how to teach it over the years, and I gratefully acknowledge their influence and impact on me and this text.

#### XII PREFACE

I also thank my colleagues at MIT, especially Jesus del Alamo, Dimitri Antoniadis, Jim Chung, Martha Gray, Leslie Kolodziejski, Harry Lee, Marty Schlecht, and Charlie Sodini, who have taught from these notes and/or who have set me straight on various issues, for their many constructive comments and suggestions. Thanks are also due to the many students who have used these notes in classes for their numerous helpful student's-eye-view comments. A particular thank you to Tracy Adams for the many hours she spent going through much of the near-final version. My thanks also to Angela Odoardi, Charmaine Cudjoe-Flanders, Karen Chenausky, and Kelley Donovan for their enormous help translating my scrawl into a presentable manuscript.

In addition, McGraw-Hill and I would like to thank the following reviewers for their many helpful comments and suggestions: Scott E. Beck, formerly of University of Arizona; currently at Air Products in Allentown, PA; Dorthea E. Burke, University of Florida; John D. Cressler, Auburn University; Robert B. Darling, University of Washington; William Eisenstadt, University of Florida; Eugene Fabricus, California Polytechnic Institute; Mohammed Ismail, Ohio State University; J. B. Kreer, Michigan State University; M. A. Littlejohn, North Carolina State University; Gerald Neudeck, Purdue University; and Andrew Robinson, formerly of University of Michigan; currently with Advanced Technology Laboratories in Bothell, WA.

Finally, I welcome further comments, suggestions, or corrections from users of this text; I invite you to communicate with me by electronic mail (fonstad@mtl.mit.edu).

Clifton G. Fonstad

## COMMENTS ON THIS EDITION (8/15/06)

The publication of this 2006 Electronic Edition of Microelectronic Devices and Circuits has been accomplished primarily as a result of the efforts of Professor Ioannis (John) Kymissis of Columbia University, a recent Ph.D. recipient from M.I.T. The author is grateful to John for helping realize this edition.

Dedicated to the memory of my father, Clifton G. Fonstad, Sr.

# CHAPTER 1

# MODELING

The title of this text is *Microelectronic Devices and Circuits*, but it is really a book about modeling. Inevitably, this focus will tend to be neglected as we concentrate on learning how semiconductor diodes and transistors work and how they are used in analog and digital circuits. Thus, it is important that we start with a few comments on models and on our hidden agenda.

# **1.1 GENERAL COMMENTS**

You are familiar with models for circuit components—resistors, capacitors, inductors, wires—and you have learned that, for example, the terminal current-voltage relationship of a real resistor that you might get from a stockroom or buy at an electronics store may be represented, or modeled, by an "ideal" resistor for which  $v_{RR'} = i_R R$ , where  $v_{RR'}$  is the voltage difference between the two terminals of the resistor,  $i_R$  is the current into the positive reference terminal (and out the negative terminal), and R is the resistance of the resistor, in units of ohms ( $\Omega$ ). We tend to think of this model when we encounter an actual resistor, and the distinction between a real resistor and the model becomes blurred. This is all right as long as we do not lose sight of the fact that v = iR is just a model, and that as such it has limitations. For example, if we change the temperature of a resistor, its Rvalue will change, and at very high current levels, the variation of voltage with current is no longer linear, in part because of internal heating. An important part of learning a model is learning its limitations, and an important part of using a model is remembering that it has limitations and knowing what they are.

In this text, one of our objectives is to develop accurate models with as few limitations as possible. We also want models that are useful. By "useful" we mean models that are analytical and, often, that are easy to use in hand calculations. We

1