Power Electronics Semiconductor Devices Edited by Robert Perret Copyright © 2009, ISTE Ltd.

## Chapter 4

# Silicon Carbide Applications in Power Electronics

## 4.1. Introduction

Despite its extreme rarity in the natural state, silicon carbide was one of the first semiconductors discovered: J.J. Berzelius (the "father" of silicon) was the first to study its physical properties, in 1824. The first to exploit its electro-luminescent properties was H.J. Round, in 1907 [ROU 07]). In 1955, Lely [LEL 55] was defining the first method of synthesizing mono-crystalline substrates, the dimensions were admittedly small and random, but had very good structural quality. Thus, the first period of intense research devoted to silicon carbide (in the USA, Russia, Japan, Germany) dates back 50 years, driven from the beginning by the very interesting physical properties of this material for solid state electronics.

Yet it is only recently (in 2000 and 2001) that the first ads for industrial manufacturing of power components, based on silicon carbide, were made (by Microsemi, then Infineon), in the form of Schottky diodes, with voltage and current ratings that now reach 600 V and 12 A. These initial products are the result of works revived and expanded throughout the world in the 1980s, thanks to new major discoveries in the field of manufacturing techniques usable by the industry. Despite the tremendous growth of the silicon industry and the considerable developments already achieved, the approaching of silicon's physical limits in many applications, particularly those in power electronics, also contributes to the high level of interest

Chapter written by Marie-Laure LOCATELLI and Dominique PLANSON.

being generated for some semiconductors with large prohibited broadband energy, particularly silicon carbide.

Given the potential of power components made of the emerging silicon carbide, and those of the prototypes reported by the specialized journals, this "new" semiconductor now appears to be able to:

- favorably replace silicon in certain applications by improving the overall performance of the system (remembering that silicon is the material of choice almost exclusively for the manufacture of power components);

- to expand the fields of existing applications; or even

- give rise to new areas of use previously inaccessible for semiconductor components.

Before presenting the various potential applications of new silicon carbide (SiC) power components, this chapter will become better acquainted with the material, before describing the state of the art technology. The final section will present designs already made with SiC, SiC impact on the design and performance of systems, and will indicate the likely applications of these systems.

#### 4.2. Physical properties of silicon carbide

## 4.2.1. Structural features

Electronic applications involve devices based on semiconductor materials with crystalline structures.

The crystal structure of monocrystalline silicon is characterized by an arrangement of Si atoms along a face centred cubic network, with a mesh parameter of 5.431 Å. The structure of crystalline silicon carbide on the other hand can be described simply by stacking compact plans, each plan being a double layer of a compact plan of C atoms on a compact plan of Si atoms. The pile of a second double layer on a first one can be in two positions, different from each other and different from the position of the first level. This is obviously the same for the next level, and so on. The three possible positions for a double layer are generally named A, B and C. According to the stacking sequence (e.g. ABCB...) and its recurrence (e.g. 2 for ABABABAB... and 4 for ABCBABCBABCB...), the elementary mesh can be cubic (C), hexagonal (H) or rhomboid (R). Only one dimension of the grid (height, in the direction [0001] perpendicular to the plains, which is the axis of growth, axe c), is different from one pile to another. This way, several crystallographic arrangements may exist for the same chemical composition SiC.

This peculiarity of silicon carbide is named after polytypism (which is a polymorphism in one dimension).

170 to 200 crystallographic varieties or polytypes have been counted. Among them, few have been synthesized into the form of mono and stable materials (without inclusion of different polytypes). The polytypism of SiC also explains in part the difficulties historically found, and even today, for the production of substrates and homogenous SiC films, especially since it gives to each polytype physical properties whose ranges vary from one to another (as shown in the following section).

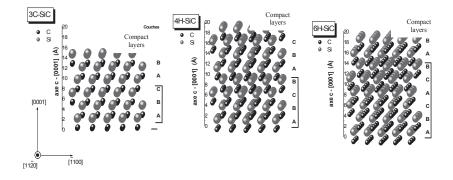

**Figure 4.1.** Presentation of polytypes SiC-3C, SiC-4H and SiC-6H, and of Ramsdell notation. This allows kinds of SiC to be distinguished by a number (stacking periodicity) followed by letter C, H or R (form of the elementary mesh)

| Polytype                                | 3C        | 4H                     | 6Н                     |

|-----------------------------------------|-----------|------------------------|------------------------|

| Stacking sequence                       | ABC       | ABCB                   | ABCACB                 |

| Mesh parameters (Å)<br>Si : a = 5.431 Å | a = 4.349 | a = 3.073<br>c = 10.05 | a = 3.081<br>c = 15.12 |

Table 4.1. Characteristic dimensions of crystalline meshes of SiC-3C, SiC-4H, SiC-6H and Si, at 300 K

The most common polytypes studied for electronics are known as SiC-3H, SiC-4H, SiC-6H, according to the notation of Ramsdell. Figure 4.1 illustrates these three structures and the principle of Ramsdell notation. Table 4.1 shows for each polytype

the specific dimensions of their crystal mesh at room temperature, as well as those relating to silicon.

## 4.2.2. Chemical, mechanical and thermal features

The link between the Si atom and the C atom is strong, with an energy equal to 6.34 eV (the binding energy between two atoms of silicon is only 4.63 eV). This simple fact makes silicon carbide a resistant material from various points of view, and contributes to the interest for it, for various applications including electronics. This property, however, includes drawbacks for the implementation of the SiC semiconductor.

Firstly, SiC is high temperature resistant, breaking only at 2,830°C. Sublimating rather than melting under reasonably accessible pressure, silicon carbide cannot be synthesized from the liquid phase by conventional techniques of recrystallization. The growth of a single crystal is more delicate than that of silicon, especially as the resulting crystalline arrangement is very sensitive to the conditions of temperature and pressure.

Silicon carbide is also chemically resistant, and it is very difficult for a foreign atom to penetrate the network of this material to travel inside. An input of energy (e.g. heat, photonics, electrical, or mechanical, etc.) higher than the case of silicon is necessary. In terms of temperature stability, these features are assets for operation in hostile environments and for reliability, but they do not facilitate the steps of production of components based on chemical reactions (cleaning, engraving, oxidation) or diffusion of impurities.

Since Acheson developed the first manufacturing process of SiC, in the 19th century, silicon carbide has been well known for its mechanical resistance as an abrasive n the form of clusters of hexagonal mono crystals, impure and from various polytypes and sizes). This hardness (about three times that of silicon), which is not really a superiority for electronic applications, is reported here because it has an effect on mechanical treatments, such as cutting and polishing units in the manufacture of semiconductors for electronics.

In terms of thermal expansion, the coefficient of silicon carbide  $(4x10^{-6} \text{ K}^{-1})$  is approximately two times greater than that of Si, which increases the gap with that of silica  $(5.5x10^{-7} \text{ K}^{-1})$ , but reduces to that of copper  $(17x10^{-6} \text{K}^{-1})$ , or aluminium  $(22x10^{-6} \text{ K}^{-1})$ .

## 4.2.3. Electronic and thermal features

As referred to in the introduction of this chapter, the attraction to the physical properties of silicon carbide for use in electronic applications is at the heart of many studies that have been, and are now doomed. The vast majority of these studies concern the three most common polytypes: 3C-SiC, 6H-SiC and 4H-SiC. Many publications present measurements and modelling parameters of these materials, and some properties are nowadays accurately determined (such as the forbidden energy band, or the effective masses, etc.). However, due to sensitivity to the purity of the material, or its anisotropy, some parameters are fairly dispersed or incompletely determined (e.g. mobility and saturation speeds of load porters, especially holes; or critical breakdown field, etc.). Table 4.2 brings together the main important features for the performance of semiconductor components. The values given are trying to account for dispersions, being an average of the main results of edited measures, for a temperature of 27°C, and for a doping of 10<sup>15</sup> cm<sup>-3</sup>. All three SiC polytypes, with whom structure tests were performed, are considered here along with silicon, as a benchmark. For hexagonal polytypes, the values of mobility and speeds of load porters are provided for both parallel directions (||c|) and perpendicular ( $\perp c$ ) to the axis of growth c.

|                                                                         | Si              | 3C-SiC | 6H-SiC                   | 4H-SiC                                                      |

|-------------------------------------------------------------------------|-----------------|--------|--------------------------|-------------------------------------------------------------|

| E <sub>g</sub> (eV)<br>Forbidden bandwidth                              | 1.12            | 2.2    | 3.02                     | 3.26                                                        |

| E <sub>c</sub> (MV/cm)<br>breakdown electric field                      | 0.28            | 1.5    | 2.2                      | 2.2                                                         |

| ε <sub>r</sub><br>dielectric constant                                   | 11.8            | 9.66   | 9.7                      | 10                                                          |

| $\mu_n$ (cm <sup>2</sup> /Vs)<br>intrinsic mobility of electrons        | 1350            | 900    | 400 (⊥c)<br>90 (    c)   | 800 (⊥c)<br>1,000 (    c)                                   |

| μ <sub>p</sub> (cm <sup>2</sup> /Vs)<br>intrinsic mobility of holes     | 480             | 40     | 100 (⊥c)<br>20 (    c)   | 110 (⊥c)<br>140 (    c)                                     |

| v <sub>sat</sub> (10 <sup>7</sup> cm/s)<br>saturation speed of carriers | 1               | 2.5    | $2(\perp c)$<br>0.2(  c) | $\begin{array}{c} 2.2  (\bot c) \\ 0.33  (  c) \end{array}$ |

| n <sub>i</sub> (cm <sup>-3</sup> )<br>intrinsic concentration           | $1.4 x 10^{10}$ | 6.9    | 2.3x10 <sup>-6</sup>     | 8.2x10 <sup>-9</sup>                                        |

| λ <sub>th</sub> (W/cm.K)<br>thermal conductivity                        | 1.5             | 4.9    | 4.9                      | 4.9                                                         |

**Table 4.2.** Main physical properties for components performances: comparison of most common SiC polytypes and silicon (values at 300 K for doped materials at  $10^{15}$  cm<sup>-3</sup>)

#### 4.2.3.1. A large forbidden energy bandwidth

Silicon carbide is part of the family of semiconductors known as "big gap" because of its *prohibited energy bandwidth*  $E_g$ , which is higher than that of silicon (2 to 3 times according to the polytype). Two other important properties follow on from this, which are a higher *breakdown electric field*  $E_c$  (almost multiplied by 10), and a lower *concentration of intrinsic*  $n_i$  *load carriers* (9 to 19 orders of magnitude depending on the polytype).

#### 4.2.3.1.1. Improvement of the voltage and temperature strengths

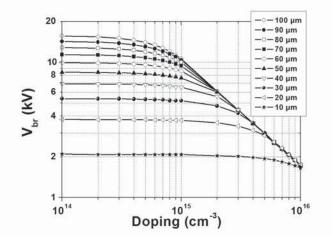

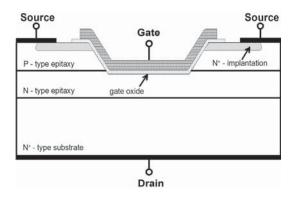

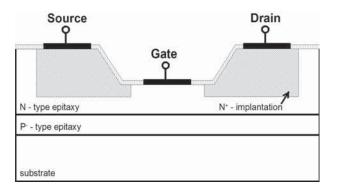

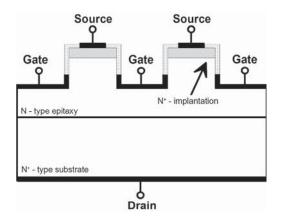

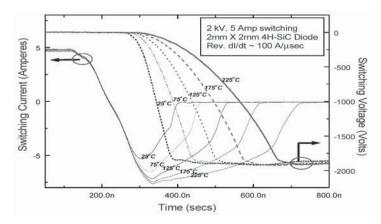

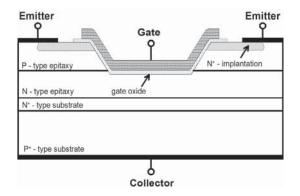

With such features, silicon carbide makes it possible to increase the range of blocking voltages allowed by the semiconductor components, and this includes at high junction temperatures. Indeed, breakdown voltages, exceeding 10 kV in volume, can be supported by layers with doping levels between  $10^{14}$  cm<sup>-3</sup> and  $10^{15}$  cm<sup>-3</sup>, and thicknesses as low as  $70 \,\mu\text{m} - 80 \,\mu\text{m}$ , as shown in the charts presented in Figure 4.2.

**Figure 4.2.** Breakdown voltage  $V_{br}$  (V) as a function of doping  $N_D$  (cm<sup>-3</sup>) and thickness  $W_N$  ( $\mu$ m) of the voltage submitted layer, providing numerical calculation of the inverse characteristic, and taking into account ionization coefficients per impact provided [KON 97]

Recall that the breakdown mechanism is the ionization of an atom of the network, by impact with a free carrier greatly accelerated by the local electric field. If the kinetic energy gained by such a carrier is enough, it can "obtain" an electron from the top of the valence band to the bottom of the conduction band, leaving a vacancy in the valence band called a hole. A new electron-hole pair is created, which will be able to participate to the increase of the reverse current through the

structure (possibly generating, in turn, an electron-hole pair by ionizing collision, thus contributing to the increasing number of load carriers).

Charts in Figure 4.2 provide the breakdown voltage in volume of a plane structure  $P^+NN^+$ , with dissymmetric and abrupt junctions. The breakdown voltage is calculated numerically and corresponds to the voltage where the multiplication factor of holes or electrons becomes infinite along a line of maximum field in the structure. The calculation is made according to the slight doping of the central layer slight N doped (the "voltage held layer"), for different thicknesses, and at a uniform temperature of the semiconductor equal to 300 K; having retained as a coefficient the values of ionization of electrons and holes published by Konstantinov *et al.* [KON 97].

Calculations of leakage currents through the  $P^+NN^+$  structure in the opposite polarization, as a function of temperature, also show that the leakage currents associated with the thermal generation assisted by inherent pitfalls porters in the deserted area ( $J_{gen}$ ), and with the diffusion of minority carriers from the adjacent neutral areas ( $J_{dif}$ ), remain low in the case of silicon carbide up to a very high temperature.

| Concentration of intrinsic carriers in a semiconductor of gap $E_g$ : where $N_C$ and $N_V$ are state densities in conduction and valence bands, and where T is temperature | $n_i = (N_C.N_V)^{1/2}.exp(-E_g/2kT)$                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| <b>Thermally generated current in the state charge</b><br><b>area:</b> in which width is $W_N$ , with $\tau$ rate of<br>generation, and q elementary charge                 | $J_{g\acute{e}n}=q.n_i.W_N\!/\tau$                              |

| <b>Diffusion current of holes from N zone:</b> with doping $N_d$ , with $\mu_p$ and $\tau_p$ mobility, and lifetime of holes                                                | $J_{dif} = (qk.T)^{1/2} . (\mu_p / \tau_p)^{1/2} . n_i^2 / N_d$ |

**Table 4.3.** Intrinsic concentration of carriers and volume leakage current through $a P^+N$  junction (abrupt and dissymmetric) under reverse polarization

For example, an analytical assessment (from the relationships mentioned in Table 4.3) of  $J_{gen}$ ,  $J_{dif}$  and of evolution in temperature of intrinsic concentration  $n_i$ , shows that we should reach 600°C, in the case of the SiC polytype 4H, so that the density of total leakage current exceeds 1 mA.cm<sup>-2</sup>, in a deserted layer, with a thickness  $W_N = 100 \ \mu m$ , which is doped at  $N_d = 10^{15} \ cm^{-3}$ , and where the time constant of carriers generation would be equal to  $\tau = 1 \ \mu s$  (considered as independent from temperature).

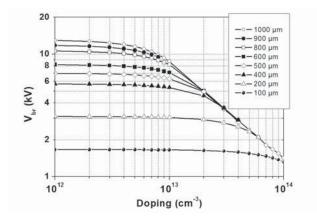

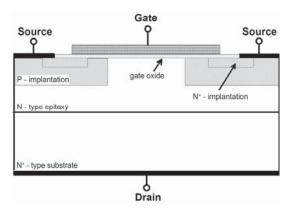

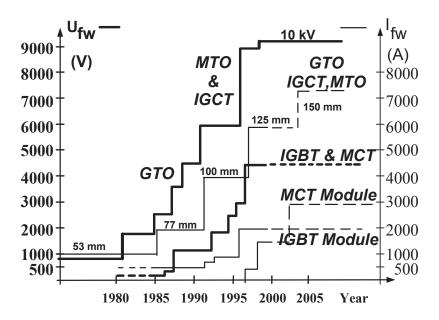

For comparison, in the case of silicon, the purest and thickest layers produced nowadays are characterized by thicknesses and doping slightly below 1 mm and  $10^{13}$  cm<sup>-3</sup> respectively. The maximum corresponding voltage ratings (in volume) reach 10 kV maximum, as can be seen on the charts in Figure 4.3. A P<sup>+</sup>N<sup>-</sup>N<sup>+</sup> structure with a "voltage holding" layer with the characteristics mentioned above, considering carrier lifetime is maintained at a high value of 100 µs, must operate with a junction temperature below 150°C, so that the leakage current does not exceed a density of 1 mA.cm<sup>-2</sup>. Note: a decrease of lifetime (including concerns about giving more rapid features to the structure during commutations between onstate and off-state) would lead to a severe reduction of this temperature (50°C less for a decrease of  $\tau$  by a factor of 10 only...

**Figure 4.3.** Breakdown voltage  $V_{br}$  (V) as a function of doping  $N_D$  (cm<sup>-3</sup>) and thickness  $W_N$  ( $\mu$ m) of the layer of Si under voltage, provides the numerical calculation of the reverse characteristic, taking into account the impact ionization

So the progress made by the silicon carbide due to a forbidden energy band is broader (resulting in a higher breakdown electric field), and appears to be significant in terms of increased voltage ratings and the setback of the allowable operating temperature limits, if considering physical properties of the material in volume; and ideally free of defects.

#### 4.2.3.1.2. Note about bipolar components

We should note that prohibited energy bandwidth also means a higher barrier of the PN junction. It will be more necessary to apply an extra 2 V to the terminals of a homo-junction of 4H-SiC, than to a homo-junction of silicon, to achieve the onstate. However, for applications with very high voltage, as considered in this part, this drawback will not present a drawback for bipolar components.

#### 4.2.3.2. Sufficiently mobile load carrier

Let us now consider the range of voltage ratings already covered by components made of silicon, and consider the fact that the higher *breakdown field* of SiC leads to the ability to withstand a voltage under switch-off state, with a semiconductor layer whose doping is higher for a lower thickness. In addition to the reduction of the corresponding dimensions (interesting itself), this is especially relevant in terms of reducing conduction losses, all the more important since the *mobilities* ( $\mu_n$  and/or  $\mu_p$ ) of load carriers involved in the mechanism are high.

Expressing these concepts with numbers, Table 4.4 shows the relative values of the factors of merit introduced by Baliga to indicate the interest in a new material for the design of a unipolar high-voltage component, minimizing conduction losses (with the BFM [BAL 82]), or the switching losses (with the BHFFM [BAL 89]). These values are normalized by those of silicon and allows a N-type conduction either lateral (perpendicular to the c axis), or vertical (parallel to the axis c), to reflect the anisotropy of the physical properties of 6H and 4H polytypes. (Note: the crystal structure 3C-SiC has no anisotropy in terms of its physical properties, as it is cubed). Note only the resistance of the layer of holding voltage is taken into account when calculating conduction losses.

This table shows again that significant progress is expected from the use of silicon carbide for the manufacture of high-voltage unipolar components. According to this "first order" assessment, the 4H polytype is the most promising, both for structures with vertical conduction and with lateral conduction.

We can greatly reduce the compromise between high current density in the onstate and high voltage rating, and increase the voltage range of unipolar components. From 200 V (maximum voltage rating with Si), the voltage ratings of Schottky diodes could be extended up to 3 kV. As unipolar devices (Schottky diodes such as field effect transistors) commutate faster than bipolar devices, a step forward in terms of reduced switching losses and increased switching frequencies of operating systems, which result at the same time.

| Merit factor                  | 3C-SiC | 6H-SiC    | 4H-SiC       |

|-------------------------------|--------|-----------|--------------|

| BFM / BFM (Si)                | 4      | 4.5 (⊥c)  | 12 (⊥c)      |

| where $BFM = \pi \mu_n E_g^3$ |        | 1 (    c) | 14.9 (    c) |

| BHFFM / BHFFM(Si)             | 16     | 15 (⊥c)   | 31 (⊥c)      |

| where $BHFFM = \mu_n E_c^2$   |        | 3.5 (  c) | 38 (  c)     |

Table 4.4. Merit factors by B.J. Baliga for SiC common polytypes,

divided by the corresponding values in the case of silicon (notations and values of physical parameters from Table 4.2 were used for these calculations) For the highest voltage ratings, the possibility of modulation of the electrical resistivity of the voltage held layer makes the bipolar device a more attractive option. In the case of bipolar components in SiC, the large voltage drop across the terminals of the PN junction (as a result of the broad band of prohibited energy) will be less of a drawback, for a given voltage class, as levels of current densities and frequency of the application will be higher. These conditions of use are promoted by both the ability of these devices to operate at high temperature, and to switch quickly.

## 4.2.3.3. A high speed to saturation

Under strong electric field (over some  $10^5$  V/cm), the drift velocity of electrons and holes tends towards a limit value. This *saturation speed*  $v_{sat}$ , which is twice as fast with silicon carbide, is still in its favor compared to silicon, for application on power components working at a high frequency.

| Merit factors                           | 3C-SiC | 6H-SiC    | 4H-SiC    |

|-----------------------------------------|--------|-----------|-----------|

| JFM / JFM (Si)                          | 156    | 215 (⊥c)  | 260 (⊥c)  |

| where JFM = $v_{sat}^2 E_c^2 / 4 \pi^2$ |        | 2 (    c) | 6 (    c) |

Table 4.5. Merit factors by E.O. Johnson for common polytypes of SiC, divided by values for silicon (notations and values of physical parameters from Table 4.2 were used for these calculations)

An idea of the expected gains is rendered by Johnson's figure of merit of (JFM [JOH 63]), whose values are presented in Table 4.5. These performance gains are very important, especially for the two hexagonal polytypes, when the electronic conduction is perpendicular to the axis of growth c.

#### 4.2.3.4. A high thermal conductivity

Losses in the components (both during their conduction or commutation phases) are an internal source of heating. When they cannot (for one physical intrinsic reason), or should not (to meet their immediate environment) work beyond a certain temperature, the ability of the device to dissipate heat is a desired quality, starting with the semiconductor itself. The latter is also appreciated when the structure is sensitive to the presence of hot spots, to reduce the temperature deviations by spreading better heat fluxes. With a thermal conductivity about three times higher than that of silicon, silicon carbide offers prospects for improvement in this regard.

#### 4.2.3.5. More generally (at the system level) and abstract

The benefits of using silicon carbide as the basic material for the manufacture of components for power, have been mentioned above:

- the rise of voltage;

- the rise in temperature;

- reducing the size;

- minimizing losses;

- the increasing frequency;

- the rising power.

These gains at the component level obviously have an impact on the performance of the system into which the component will fit. In particular, silicon carbide allows for the consideration of a greater density of system integration with smaller components, whether active or passive (including inductive elements working at higher frequencies), and the prospect of less complex systems (with fewer series or parallel connections, or simplification of the problems of adaptation of impedance, or problems of cooling, etc.).

In summary, considering the elements presented above, silicon carbide satisfies theoretically the first clauses for an alternative solution to replace an existing and already very well established solution: to obtain a significant gain on the performances of many systems. We will further see that sectors previously out of the reach of silicon may even be involved.

## 4.2.4. Other "candidates" as semiconductors of power

In fact, outside the silicon, only gallium arsenide (GaAs) is the subject of sales of slices (up to 150 mm diameter), and the market for telecommunications systems implementing GaAs components is booming. however, this material progress appears inadequate next to that of silicon, and to the needs of power systems to allow a significant place for this material.

Other semiconductor materials, such as diamonds, or some nitrides, particularly GaN, are also alternatives that are currently being researched [CHO 00], because they present the potential for a major increase in the level of performance for power electronics, sometimes earning well above what has been described for SiC. Nevertheless, they do not comply with yet another essential clause for the emergence of a new industrial application: the availability of mono-crystalline

substrates of sufficient size and quality. The major obstacles have not yet all been removed in terms of the mastery of basic techniques required for the achievement of a semiconductor component on the basis of these materials, such as control of the conductivity (type N or P) by doping, etching, metallization of contacts, filing of dielectric or encapsulation.

Instead, the maturity of the technology in the industry based on silicon carbide, especially for 6H and 4H polytypes, is already sufficient to enable the emergence of the first power components on the market. The following section gives state of the art expertise on the components acquired at various stages of manufacture, as well as on the main areas of current research.

#### 4.3. State of the art technology for silicon carbide power components

In this section we briefly describe, as a priority, the techniques adopted by the industry, or most commonly used by research centres. The technology of silicon is mentioned to highlight the differences or the similarities between the two chains.

The characteristics able to assess the level of quality achieved at each stage of the development of a component are mentioned. Those characteristics likely to have an impact on the proper operation of the devices are primarily selected, in order to understand their performances in the final part. We are also trying to provide an overview of the derivative of progresses.

## 4.3.1. Substrates and thin layers of SiC

Three among many identified polytypes of silicon carbide, were able to be synthesized in the form of massive monocrystalline materials, used in the manufacture of electronic components: they are chronologically 6H-SiC, 4H-SiC, and very recently 15R-SiC. These materials are prepared to be used as substrates, on which thin films are implemented for devices realization. Only substrates 6H-SiC and SiC-4H, epitaxial or not, are commercially available. Note that 6H-SiC N-type also has a broad market potential as a GaN substrate for the production of electroluminescent components.

As this section reports, synthesis techniques of SiC are much more sensitive than those of silicon, this justifies the historical difficulties, and suggests that the cost of this type of material is likely to remain high.

## 4.3.1.1. Monocrystal growth for the production of substrates

## 4.3.1.1.1. Roles and qualities expected

The substrate serves mostly as mechanical support around which will be deposited the various films (single-crystal film, insulation or metal) to make the final device. In silicon technology, when the voltage rating requires a layer of semiconductor very thick and lightly doped, it can be produced by the substrate itself. In all cases, the structural properties, electrical and thermal, of this substrate are very important, as an integral part of the structure.

#### 4.3.1.1.2. Technical production and marketing

The commercialization of the SiC material dedicated to microelectronics began in the USA in 1989. The company CREE Research proposed slices of 6H-SiC of 25.4 mm in diameter. Today several vendors ([CRE 01a], [STE 01], [OKM 01], [NIP 01], [SIX 01], [SICr 01]) of platelets of 6H SiC up to 76.2 mm diameter and 4H-SiC up to 50.8 mm diameter are present on the world market (Finland, Japan, Germany, and always the USA).

The most common growth technique is based on the vapor phase transport of the chemical species involved, obtained by sublimation of a source of SiC material in the 2,200-2,500°C range, therefore high if the reference is once again that of silicon, followed by condensation on a germ of monocrystalline SiC, introducing the polytype desired. The germ is placed near the source and brought to a temperature slightly below the temperature of the source (the pressure inside the crucible is in the order of 10 to 50 Torrs). The speed of growth by this technique is in the order of several mm/h.

A monocrystalline ingot of a few centimeters in height is obtained by this method, also known as the "Lely modified" (originally discovered by Tairov and Tsvetkov [TAI 78]). The ingot is then rectified in the form of a cylinder to provide slices after sawing and polishing (which are non-trivial steps because of the hardness of the material).

#### 4.3.1.1.3. Current characteristics

In addition to controlling the polytype (by the nature of the germ), the growth of massive SiC by this technique allows control of the size, structural quality and electrical conductivity of the substrate produced.

In regards to the crystalline quality, which has been making constant progress in recent years, typical values and best results characterizing the major flaws existing in the marketed silicon carbide substrates are presented in Table 4.6. Only those defects inducing an impact on the quality of epitaxied films on these materials are

cited. (For example, parallel dislocation loops to the base plane of the substrate, present in very high density but which do not propagate in the epitaxial layer, are not included in Table 4.6 [NEU 00].) It is also known that the material still contains many chemical impurities.

The resistivity of the semiconductor is also controlled for the growth of the monocrystal, by incorporation of doping atoms (nitrogen for N and aluminum for P). The heavily doped substrates required for the manufacture of components for power electronics, have resistivities that vary between suppliers. We can find, for example, 15-30 m $\Omega$ .cm for the 4H-SiC N-type and 2.5-8.5  $\Omega$ .cm for 4H-SiC P-type (corresponding to the doping of some 10<sup>18</sup> cm<sup>-3</sup>). Several substrates 6H-SiC or 4H-SiC, semi-insulating materials, are also available from some manufacturers, primarily dedicated to the market of power microwave components. The resistivities in these cases are above 10<sup>5</sup>  $\Omega$ .cm.

It should be noted that the thermal conductivity of the material is affected by the crystalline quality: it is typically 3 to 3.8 W/cm.K (at room temperature) for the traded substrates, compared to 4.9 W/cm.K measured for the purest substrates (produced by Lely's method).

| Type, nature of defects                      | Density or % of the surface of<br>the substrate    |

|----------------------------------------------|----------------------------------------------------|

| Micro pores<br>(or dislocation opened screw) | $< 30 \text{ cm}^{-2}$                             |

| dislocations closed screw                    | $3,000 \text{ cm}^{-2}$ to 10,000 cm <sup>-2</sup> |

| Hexagonal form plates                        | < 10 %                                             |

| Small growth cavities<br>(orange skin)       | < 10 %                                             |

| inclusions (polytype 3C,)                    | < 5 %                                              |

Table 4.6. Typical data from CREE [CRE 01a] for SiC substrates (50.8 mm diameter) of

"Production" quality (qualified area corresponds to the whole surface of the slice, excluding a border of 2 mm width)

## 4.3.1.1.4. Avenues of research

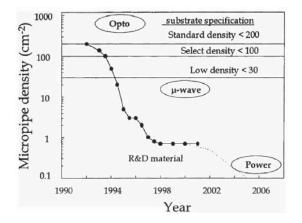

The process of growth is the subject of much research to improve the ingot's quality [ANI 99]. Further progress is required to reduce the density of defects in large-diameter substrates, in order to increase yields and reduce manufacturing costs, both of the base material and components that will use it. Diameters of up to 100 mm have been demonstrated in the laboratory, along with micropore densities of less than 1 cm<sup>-2</sup>. With regard to this type of defect, Figure 4.4 [HAR 01]

illustrates the evolution of their presence in recent years, as well as the changes expected for the future: according to these forecasts, obtaining the required densities for the production of large-scale power components (for ratings in currents beyond 100 Amps) should occur around 2005.

In parallel to these studies for optimization by the "classical" method, alternative techniques provide material of good crystal quality, such as chemical vapor deposition at high temperature (HTCVD) [ZHA 01], or liquid phase epitaxy (LPE) [REN 98], are investigated, with the goal of increasing their deposit rates (which are currently in the order of several hundred  $\mu$ m/h). We would like also to mention that the HOYA Corporation [HOY 01] has presented at the International Conference ICSCRM 2001, a slice of 3C-SiC of 100 mm diameter, produced by hetero epitaxy on a silicon substrate, eliminated thereafter [NAG 01]. The main characteristics of this material are a thickness of 200  $\mu$ m, a density of crystalline defects less than 10 cm<sup>-2</sup> with no micropores, and a level of doping (N or P type) from 10<sup>15</sup> cm<sup>-3</sup> to 10<sup>19</sup> cm<sup>-3</sup>. 3C-SiC substrates are even marketed at a very attractive price.

**Figure 4.4.** Temporal evolution of the defect density of micropore type, in substrates elaborated in laboratories by the "modified Lely method" (figure from [HAR 01]). The authors indicate the required levels for commercialization of optoelectronic components, microwaves or power, together with specifications of substrates by the supplier CREE

#### 4.3.1.2. Obtaining monocrystalline thin films

#### 4.3.1.2.1. Roles and expected qualities

The active parts of a component are generally in "thin" semiconductor layers filed to that effect on the substrate. This substrate typically has a thickness of  $350 \,\mu\text{m}$ , which is necessary to give an overall mechanical rigidity sufficient for

manipulation. The N-type or P-type layers needed for the construction of the component, in fact, have a thickness which can vary over a wide range (orders of magnitude ranging from 100 nm to the nearest hundred  $\mu$ m). This thickness, which depends on the role of the layer within the component and also the voltage rating of the device must be controlled precisely. Another important feature if the deposited film is to be controlled finely is its resistivity. In addition to these two quantities, the quality of the crystal layer, must be uniform over the entire surface of the layer. The number of suppliers of epitaxial substrates is smaller than that of simple substrate providers. Some component manufacturers also have their own in-house source.

## 4.3.1.2.2. Techniques

In this section, we will consider the homoepitaxy of 6H-SiC and 4H-SiC by CVD, which is the only technique used industrially today. We also discuss homoepitaxy of 3C-SiC and the postponement of SiC films on various substrates, for the economic interest they represent, although these processes are still at the research stage.

## Homoepitaxy

The technique currently used by industry is the chemical vapor deposition. The growth takes place at a temperature between 1,400°C and 1,600°C, sweeping a gas rich in species Si and C, on a substrate with a disoriented surface from the axis c [KOR 98].

This disorientation of the surface (from 3.5° for the polytype 6H, and 8° for the polytype 4H) provides an homoepitaxial layer without inclusions of parasitic polytypes (epitaxy called "steps control "). The mastery of the process also helps to prevent the increase of micropore densities and other dislocations compared to those of the starting substrate.

The growth rate is relatively low (2 to 5  $\mu$ m/h) for basic systems, but heavy thicknesses are available thanks to the new hot-wall systems allowing high velocity deposition (50  $\mu$ m/h).

The unintentional conductivity of the films produced by this process is N type, with a level of residual doping between  $10^{13}$  cm<sup>-3</sup> and  $10^{14}$  cm<sup>-3</sup>. The mastery of the resistivity is in a range of  $10^{15}$  cm<sup>-3</sup> to  $10^{19}$  cm<sup>-3</sup>, and is produced by the incorporation of the doping impurity in the gas source (nitrogen to get the type N and aluminum for the P-type) during the epitaxy, and control of the mechanism of site competition [LAR 97].

The commercial buildings have improved the uniformity of thickness and doping layers (typically equal to 10% for doping) by rotating platelets in the flow of gas,

while allowing for the simultaneous processing of multiple wafers [EPI 01]. It is worth noting, however, that uncertainty about the actual value of the thickness of a commercial epitaxy remains high (up to 25% if less than 1  $\mu$ m, and 10% if over 10  $\mu$ m), and that the constancy of doping throughout the thickness of a layer is not specified. This can be a significant source of error in assessing the performance of a component, in particular whether it should be "high voltage".

The lifetime of minority charge carriers is a highly sensitive parameter to the purity (structural, chemical) of the semiconductor, and also critical for the smooth operation of bipolar components. The maximum values published for the lifetime of holes in the thick SiC epitaxies have increased in recent years, in agreement with the simultaneous improvement of the quality of substrates and epitaxies, reaching levels in the order of several microseconds [KOR 96]. We will see in section 4.4 that these materials allow for bipolar devices (diodes) with low differential series resistance, and high speed.

The various possible consequences of the present imperfections of epitaxies (mainly induced by the substrate) on the final characteristics of power components are under investigation. Some are already well known, like the premature breakdown of the components due to the micropores, which propagate from the substrate through the thickness of the epitaxial layer. The best current densities of these defects (1 cm<sup>-2</sup> for substrates of 50.8 mm in diameter, see Table 4.6) already allow for the use of some high-voltage devices sized in the order of 10 mm<sup>2</sup>. The polytypes inclusion, or surface defects, will also affect the inverse characteristics (blocking of bipolar junctions or Schottky) or direct characteristics (channel conduction of MOSFET transistors). The frequency of these defects is already relatively low and on the decline. However, the screw dislocations present in much higher densities (also spread throughout the thickness of the epitaxy) worry today's designers more because of their impact on the current and electrical behavior in the vicinity of the breakdown voltage. While it has changed little in recent years, a dislocation density of less than 1,000 cm<sup>-2</sup> would be required to obtain power components. It should be noted that the silicon wafers, which are at the foundation of existing devices, have dislocation densities within this order of magnitude.

In addition to a constant search for improving the chemical and crystalline quality of epitaxial films (but first of all through an improvement in the substrates), the concerns of scientists focus on increasing deposit rates, while preserving the control and uniformity of low doping (about  $10^{14}$  cm<sup>-3</sup>), with the main objective of meeting the needs of power electronics. The technique of chemical vapor deposition at high temperatures (up to 2,000°C), must also be mentioned, with which growth speeds as high as 800 µm/h were obtained [ELL 00].

#### Other techniques (at the research stage)

Because good quality substrates (6H-SiC, 4H-SiC) are expensive and small (though the latter tends to reduce grievance), or because they are still lacking (as for 3C-SiC), the search for obtaining monocrystalline of SiC films on various other substrates have continued.

#### *Homoepitaxy by heteroepitaxy*

The absence of substrates (except of small ones, mainly of 6H polytypes, obtained by the Lely method), largely contributed to research efforts into heteroepitaxy of SiC on silicon, with first interesting results appearing at the beginning of the 1980s [NIS 83]. The obtained polytype was 3C-SiC, which has the lowest disagreement mesh with Si.

The physical properties of this polytype (particularly in terms of mobility of carriers), have kept the interest of this research despite the emergence of 6H-SiC substrates onto the market in early 1990. Today, the main interest of such research into power electronics, while substrates and thin layers of 4H-SiC are available, is primarily economic (reduced cost of silicon and manufacturing stages on this substrate of "standard" size). The 3C-SiC materials owns good factor of merit (as shown in section 4.2) relating to obtaining vertical conduction, and fast devices. Applications outside the field of power electronics (particularly as sensors in hostile environments – temperature, radiation) also contribute significantly to the research efforts.

Due to differences in parameter mesh (of 20%), and coefficients of thermal expansion (8%), the films of 3C-SiC deposited on silicon contain crystalline defects in large quantities, even when a preliminary step known as "carbonization" of the silicon surface is included [MAT 88]. Some of the defects annihilate during growth, and beyond a thickness of about 5  $\mu$ m, the monocrystal is homogenous, but the density of defects is still about 10<sup>8</sup> cm<sup>-2</sup>. Growth temperatures of above 1,000°C are necessary to prevent the incorporation of micro-crystals into the layer of SiC. In addition, these films suffer important constraints that curve the substrate, or even cause cracks [CHA 01]. Thus, the electrical characteristics of the layers of SiC-3C are degraded.

## Homeopitaxy by postponing thin layers

A more recent form of research, with the same economic concerns, applies the Smart-cut process (developed by LETI/CEA [BRU 95] in conjunction with SOITEC), to provide reports on the surface of a substrate A (preferably low cost and standard dimensions): a thin layer of silicon carbide cut off on the surface of a monocrystalline substrate B. This process was first tried with success from wafers of 6H-SiC on silicon substrates [DIC 96].

The process applied to the silicon carbide is, as a first step, establishing a strong dose of hydrogen on the surface of sample B (SiC), in order to create a weakened plan, to a depth determined by the energy of implantation. The established face of this sample B is then pasted (by molecular accession) to sample A. A proper separation process (e.g. thermal), generally applied, causes a cut in the B sample to the depth of implantation, separating it from the SiC thin film transferred to sample A. Sample B can then be recycled to provide a new film of silicon carbide.

When an insulating gluing interface (for instance,  $SiO_2$  or  $Si_3N_4$ , etc.) is used, in order to form a structure called "SiCOI", the target is in addition to combine the advantages of silicon carbide and those of structures on insulator. The purpose (for power electronics) is to obtain lateral power components, or even to have an adaptive technology to achieve power integrated circuits, if the characteristics of the material transferred and of the devices which can be made permit it. The optimization of the process has now reduced the level of compensation for N-type films (resulting from the implantation of hydrogen). At the moment, 6H-SiC or Ntype transferred 4H films, used for the creation of components, have a thickness between 0.5 µm and 1 µm, and a concentration of acceptor-type defects of less than 4 x 10<sup>16</sup> cm<sup>-3</sup> [HUG 00].

When a metal interface bond is chosen, the hetero structure is created in the hope of achieving power components with vertical conduction from a "quasi substrate" of cheaper silicon carbide, called "QuaSiC" [LET 01]. The possibility of obtaining a coat of mono crystalline 4H-SiC, 8  $\mu$ m thick, created by homoepitaxy on a thin film previously transferred on a substrate of polycrystalline SiC (the bonding interface used is WSi<sub>2</sub>) has been reported.

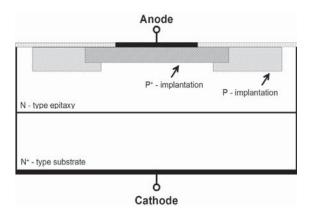

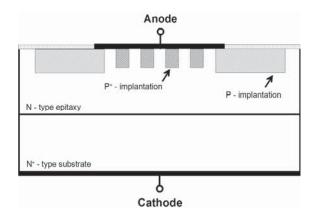

#### 4.3.2. Technological steps for achieving power components

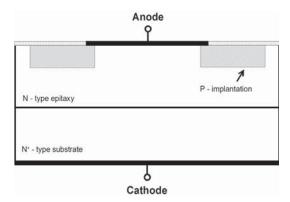

Once the required piling of thin layers on the substrate, necessary for the achievement of a component (for example: N<sup>-</sup> epitaxial growth on N<sup>+</sup> substrate to get a Schottky diode, or P<sup>+</sup> on N<sup>-</sup>, on N<sup>+</sup> substrate for a bipolar diode, or P<sup>+</sup> on N on P<sup>-</sup>, on substrate N<sup>+</sup> for a thyristor, etc.) has been achieved, a number of technological steps are necessary to complete the chosen structure and allow it to be connected and integrated into a box or a system ensuring its operation.

Two techniques traditionally used for silicon can also be used by manufacturers creating components based on SiC: these are *wet etching* and *doping by localized impurity diffusion* through a mask. Despite these two features, it was not required, in general, to develop specific equipment: the processing of wafers of silicon carbide largely benefited from the know-how and facilities developed, and became the industry standard for silicon (for example, wet etching installation, implementers,

but also oxidation or deposition installations, photolithography, etc.). Other examples are the characterization and analysis techniques that have accompanied them. This has contributed to the rapid progress of research on the components, allowing for the early opportunity to experimentally test most of the known architectures. However, great efforts have been made to develop procedures adapted to the new semiconductor, especially with regard to temperature and duration of treatment (for oxidation and ion implantation, etc.), the chemical nature of the elements (gas, dopers, metals, insulators), which are often redefined and optimized. The small size of SiC substrates also intervened significantly in the development of these procedures. An exception must however be mentioned: the stage of postannealing used for ion implantation doping of SiC implements specific furnaces, as high temperatures are required.

The following sections will review the key steps for the successful implementation of a power component of silicon carbide, in order to clarify the state-of-the-art features that underlie the performances of modern demonstrators (the results shown are for polytypes 6H and 4H).

## 4.3.2.1. Etching

## 4.3.2.1.1. Roles and qualities expected

The etching of the semiconductor is an indispensable tool, used for many purposes, such as surface treatment, the attainment of trenches, resuming buried contact, and achieving periphery (mesa), etc. Unlike in the case of silicon (or amorphous silicon carbide), the attack by wet chemistry is ineffective for a material with a high binding energy like SiC (except by molten salt at temperatures above 500°C, using unsuitable techniques for an engraving to be selective, not contaminating the structure, etc.). In the early 1980s the dissolution of this technological blockage contributed, alongside the discoveries of a method of controlled growth ("LELY amended") and a process of hetero epitaxy for 3C-SiC on Si, to renew interest in this semiconductor. This is due to the advent of plasma etching systems (developed to improve the sharpness of definition of the grounds on silicon), which were used successfully to attack SiC. Good control of the speed of etching, its selectivity towards masks and the state of the etched surface (physical, chemical and morphological) is usually required for this step.

## 4.3.2.1.2. Techniques and current features

The dry etching simultaneously results from a chemical attack and a physical attack, respectively caused by the presence of neutral reactive species in plasma (fluorine or chlorine, which react with Si, and oxygen that reacts with C, etc.) and ions accelerated to the surface to be etched ( $Ar^+$ , etc.). The "high density" etching systems of the latest generation (with a high concentration of ions) allow for etching

speeds of 100 nm/min. These speeds are sufficient to build most of the component structures, provided there is a material masking not eliminated (or distorted) throughout etching SiC. The etching selectivity represents this quality as the ratio of the attack speed of the material to be etched and that of the mask, as presented in Figure 4.5.

**Figure 4.5.** Representation of SiC etching with an angle  $\theta$ . The mask is represented in gray. After etching, the original mask is represented by the dotted line. Etching selectivity is  $V_{sc}/V_{m\nu}$ with  $V_{sc} = h_{sc}/d$  and  $V_m = h_m/d$ , for an etching duration d

The various natures (and *selectivities* of etching) of the most commonly used masks are: aluminum (> 20), silica (from 1 to 6 depending on the quality of SiO<sub>2</sub> and chemical attack process), and resins of photo litho etching (0.3 to 0.4 [MER 01]). The very low speed attack of aluminum compared to that of SiC authorizes deep engravings, with relatively vertical walls. Selectivities much lower (as in the case of SiO<sub>2</sub>) can be restrictive in terms of depth of attack, according to the feasibility of filing a thick mask. Nevertheless; they are used for obtaining etching flanks with a slope angle (angles from 30° to 80° from the horizontal, with a depth of etching of SiC of 3  $\mu$ m [LAN 96]) around 5° tested on 5  $\mu$ m [MER 01]).

The research focuses on achieving deep engravings, with controlled angle and quality etching flanks.

#### 4.3.2.2. Selective doping by ion implantation

#### 4.3.2.2.1. Roles and expected qualities

Selective doping is essential to achieve planar devices (i.e. without relief from the surface of the semiconductor), whether for the creation of emitters  $P^{++}$ , grids P,  $N^{++}$  sources, contacts ( $N^{++}$  and  $P^{++}$ ), or peripheral protections (P or  $N^{+}$ ). For the latter aspect of peripheral protection, the ion implantation is also sometimes used to locally make amorphous the semiconductor surface. Here we will only address the application concerning doping, which is to create boosted regions in a range of concentrations ranging from a few  $10^{16}$  cm<sup>-3</sup> to  $10^{20}$  cm<sup>-3</sup>, preserving a good crystalline and chemical quality, in the volume and on the surface.

#### 4.3.2.2.2. Current techniques and features

The ion implantation followed by annealing is the only feasible technique for localy doping silicon carbide (because of the prohibitive temperatures required for doping by diffusion of doping impurities). Typically, the bombing serves to incorporate the ionic doping impurities in the material at a depth dependent on the energy transmitted to the ions, the size of these, the density of the target, and its crystalline orientation from the incident beam. The high density of silicon carbide (see section 4.2.2) will result in shallower penetrations than in the case of silicon with a given implantation energy and impurity, when the direction of implementation is misaligned from any crystallographic axis. Note, however, that the structure of SiC promotes a secondary pipeline, which could lead to the creation of deformed and little steep junctions with a tail of the implementation profile. This phenomenon is more difficult to avoid than in the case of silicon [MOR 99].

Because of the very low mobility of doping impurities in SiC (their coefficients of thermal diffusion being very small), the spatial distribution of implemented impurities is generally not changed during the post-implantation annealing (boron is an exception, which has a circulation assisted by defects), while this phenomenon is often exploited in the case of Si (although also sometimes has detrimental effects). Multiple implantation with high energy (or more rarely intentionally channelled implantations) is usually implemented to achieve junctions or deep boxes (i.e. beyond  $\mu$ m) in SiC.

The post-implantation annealing is nevertheless essential to rebuild the crystal damaged during the ion bombardment, and make the implanted impurity migrate to a site for replacement of an atom of the network, so as to be an electrically active doping. In SiC, some generated defects are particularly stable. Accordingly, it is important to minimize the degree of damage of the crystal. To do so, a hot implantation is generally used when the level of referred doping requires a dose above the threshold which makes the material amorphous at room temperature. It also follows that temperatures during the consequent annealing need to be much higher than those usually used (especially for the P-type doping). These high temperatures (at least 1,700°C for Al) also require good atmospheric control to maintain a suitable surface on the samples. Specific ovens or techniques to the SiC industry are needed for this step.

|                                                                                   | N-Type                                                                    |          |                                     | Р-Туре |                                                                  |                      |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------|-------------------------------------|--------|------------------------------------------------------------------|----------------------|

| Nature of impurity                                                                | Nitrogen                                                                  |          | Phosphorus                          |        | Aluminum                                                         | Bore                 |

| Atomic mass (u.a.m)                                                               | 14.                                                                       | .003     | 30.974                              |        | 26.982                                                           | 11.009               |

| Ionization energy                                                                 |                                                                           |          |                                     |        |                                                                  |                      |

| (E <sub>A</sub> , MeV)                                                            | h                                                                         | с        | h                                   | С      |                                                                  |                      |

| for 6H-SiC                                                                        | 81                                                                        | 140      | 85                                  | 135    | 200-250                                                          | 285-390              |

| for 4H-SiC                                                                        | 42                                                                        | 84       | 53                                  | 93     | 191-230                                                          | 300-400              |

| <b>Ionized impurities at 25°C</b><br>(for $N_{A,D} = 10^{19} \text{ cm}^{-3}$ and | 70                                                                        | 70% #70% |                                     | 0%     | 2%                                                               | 0.15%                |

| $N_{comp} = 5 \times 10^{15} \text{ cm}^{-3}$                                     | (E <sub>A</sub> =0                                                        | .08eV)   | (E <sub>A</sub> =0.08eV)            |        | $(E_A=0.2eV)$                                                    | $(E_A=0.3eV)$        |

| Orders of magnitude of the                                                        |                                                                           |          |                                     |        |                                                                  |                      |

| depth of implantation (µm).                                                       |                                                                           |          |                                     |        |                                                                  |                      |

| Examples for:                                                                     |                                                                           |          |                                     |        |                                                                  |                      |

| - classical energy: 200 keV                                                       | 0                                                                         | .3       | 0.                                  | 18     | 0.22                                                             | 0.39                 |

| - high energy: 1 MeV                                                              | 0.                                                                        | .92      | 0.8                                 |        | 0.95                                                             | 1.14                 |

| Threshold to be amorphous at room temperature (cm <sup>-2</sup> )                 | 4 x 10 <sup>15</sup>                                                      |          | $\sim 2 \times 10^{15}$             |        | ~10 <sup>15</sup>                                                | 5 x 10 <sup>15</sup> |

| Implantation temperature<br>(°C)                                                  | RT – 1000                                                                 |          | RT – 600                            |        | RT –850                                                          | RT – 700             |

| Annealing temperature (°C)                                                        | 1,300-1,500                                                               |          | 1,300-1,700                         |        | 1,500-1,800                                                      | 1,500-1,800          |

| Resistance/square ( $\Omega$ / )                                                  |                                                                           | AO 98]   | -                                   | AN 00] | 285 [KIM 01]                                                     | Very high            |

| (examples, for 4H, at T <sub>amb</sub> )                                          | (N : 2.5x10 <sup>19</sup> cm <sup>-3</sup> , (P<br>thickness: 0.4 μm) thi |          | (P: 1x10 <sup>2</sup><br>thick: 0.4 |        | (Al : 1.6x10 <sup>20</sup> cm <sup>-3</sup> ,<br>thick: 0.25 μm) |                      |

Table 4.7. Characteristic quantities for the doping impurity, doping process, or the layer of SiC implanted and annealed

Table 4.7 presents the dopings which are currently used by technologists, and some characteristics of impurity, process, or either the implanted and annealed layer. Aluminum and nitrogen are respectively P-type and N-type doping, encountered in the majority of devices because they have low ionization energy compared to other impurities. While the minimum values of the N-type layers resistance implanted with nitrogen are close to the values obtained on Si [RAO 98], those of the P-type layers doped with aluminum remain very high [KIM 01].

For the P-type doping, boron is also used: its small size facilitates its incorporation. The threshold for amorphous is higher and implanted profiles are

deeper for the same acceleration energy when compared with Al, especially since during the post-implantation annealing, this impurity displays the ability to disseminate significantly, beginning at 1,400°C. However, dissemination occurs in all directions, especially to the surface (exodiffusion) [LAU 99], making the control of the incorporated dose difficult [TRO 97]. More rarely, phosphorus is used for the N-type doping, due to the improved values for electron mobility, leading to a lower resistance per square.

Finally it must be noted that an ionization energy similar to aluminum (especially that of boron) leads to an incomplete ionization of doping on a large portion of the range of operating temperatures covered. This represents an additional factor (compared to the case of silicon) and a very important consideration for the prediction or analysis of trends in temperature performance of SiC devices. The bipolar structures with a  $P^+$ -type emitter, which is dependent on an efficient injection of holes, are in particular affected by this consideration, as may be found in section 4.4.2.

## 4.3.2.2.3. Research avenues

The progress to be achieved thus lies in improving control of profiles and levels of doping, especially in the case of strong doping and P-type. From the viewpoint of implantation techniques, research teams work in particular on the implantations at high energy, to reduce damage to the crystal and therefore make it possible to increase the implanted doses [TAK 98]. The co-implantation is also considered to improve the incorporation of Al and B in substitute sites [OSH 01]. Finally, the channelled implantation (oriented along a preferred crystallographic axis) is a line of research seeking to increase the depths of implantation, while reducing damage to the crystal.

From the viewpoint of the annealing process, many studies are conducted to improve the electrical activation of doping and the quality of the crystal, not only in volume but also on the surface. For this, quality depends not only on that of doping, but also the success of subsequent manufacturing steps such as etching or more thermal oxidation. Different techniques (such as, induction furnaces [LAZ 00] or pulsed annealing [PAN 01], etc.) and various configurations of environment of samples were studied.

## 4.3.2.3. Oxidation, and deposition of insulation

## 4.3.2.3.1. Roles and expected qualities

Different functions involving the presence of an insulator in contact with the semiconductor within the components include passivation and surface protection,

insulation between the electrodes or between semiconductor areas, insulation of command grid, etc.

The silicon industry exclusively uses the product of silicon thermal oxidation,  $SiO_2$  for insulation. The excellent properties of this insulator on silicon (also accessible by certain deposit techniques) have been one of the key factors in the development of microelectronic applications based on silicon. As the thermal oxidation of silicon carbide also produces silicon dioxide, the same functions of insulation and surface passivation are desired for SiC based components. There is therefore much work towards development and optimization, as was the case for silicon. The difficulties encountered today in obtaining good electronic properties at the interface (low charge density and interface statements) are reminiscent of those encountered at the beginning of development for the MOS on silicon.

However, specific features of SiC (its nature or future use) cause new issues to arise, which require research into new methods for making  $SiO_2$ , or investigations on other insulators. The current state of knowledge is summarized here. A comprehensive and recent review [RAY 01] on this key issue can be accessed for more details.

4.3.2.3.2. Thermal oxidation (and depositing silicon dioxide)

As with silicon, the chemical reaction (in the presence of  $O_2$ , wet or dry, activated by temperatures from 850°C to 1,150°C) leads to a consumption of the semiconductor thickness equal to 45% of the thickness of the resulting SiO<sub>2</sub>. As on silicon too, the volume properties of that oxide are a refractive index of 1.45, a very good dielectric strength of 10 to 12 MV.cm<sup>-1</sup> (if obtained on dry material of good crystalline quality) and a low resistivity in the field of  $10^{14} \Omega.cm^{-1}$ . We can therefore consider this technique in terms of the same goals, namely mainly cleaning and polishing the surface by sacrificial thermal oxidation (for manufacturing techniques) and creation of an insulator (at component level, as isolated grid or protection of surface or insulation cabinet, etc.).

Note however that the use of  $SiO_2$  as insulation on SiC must take into account that the maximum values of the electric field, inside a component that are optimized to take advantage of the strengths of silicon carbide, become similar to the magnitude of the breakdown field of  $SiO_2$ . This is a new situation for the designer accustomed to the values of electric fields in Si, which remain some 20 times lower than the critical threshold for  $SiO_2$ . This will also have repercussions on the architecture or on conditions of use of components employing  $SiO_2$  as insulation.

Among the differences affecting the technological level, the first to be reported concerns the kinetics of oxidation which is much slower for SiC than for Si (for example, in the order of 10 nm/h by dry oxidation at 1,150°C, and for Si in the order

of magnitude of 300 nm/h by dry oxidation or 4  $\mu$ m/h during wet oxidation at 1,100°C), which will restrict the ability of this process to achieve preferably thin oxides, such as grid oxides or primary passivation. While remaining of the same order of magnitude, speed of growth of the oxide on a given polytype of SiC varies significantly depending on the crystalline orientation of the surface (kinetics is the fastest on face Si, slowest on face C, and intermediate on the other sides), and its level of doping. Note also that a damaged crystal (for example, by an ion implantation) oxidizes more easily than the blank crystal, in particular the oxidation of amorphous silicon carbide is much faster than mono crystalline SiC. To obtain relatively thick layers or uniform thickness over a surface with regions of different types, processes for implantation of SiO<sub>2</sub> previously developed for Si are used (for example, to make ion implantation masks or plasma etching).

The second difference is a current difficulty that exists when dealing with the quality of the interface between SiO<sub>2</sub> and SiC. This is lower than that obtained on silicon, in terms of effective charge density and the density of interface states, as well as potential fluctuations in the interface, this includes the quality of "first choice" commercial material. These three quantities (the values still widely dispersed) are indeed usually greater than those obtained today with silicon. Wet oxidations at a temperature exceeding 1000°C and some processing of the surface before oxidation, and annealing after oxidation, have recently helped to reduce them [LIP 98]. In general, it is noted that oxides on the silicon face of SiC exhibit an effective charge density lower than that of the carbon face (best value:  $2x10^{10}$  cm<sup>-2</sup>). The density of interface states, remains currently higher on the 4H-SiC polytype [AFA 00] (around 10<sup>12</sup> cm<sup>-2</sup>.eV<sup>-1</sup>). And what is more, implanted P-type materials are penalized even further. Now the MOSFET in 4H-SiC with N channel inversion in an implanted P box is expected to be "flagship" structure achieving SiC transistors (as shown in section 4.2.3.2). Apart from non-ideal threshold voltages, these structures suffer from an apparent mobility of the electrons in the channel inversion, well below its theoretical value of temperatures around 150°C (the gap is reduced when temperature increases). The channel mobility of electrons is generally less than 25 cm<sup>2</sup>.V<sup>-1</sup>.s<sup>-1</sup> for SiC-4H at room temperature, while being two to three times greater for SiC-6H. The interface statements of acceptor type located at energy levels very close to the bottom of the conduction band [SCH 99], as well as the sharp fluctuations of the surface potential [OUI 97], seem to be recognized today as contributing to the high resistivity of the inversion channel. The deposited oxides do not solve this major problem (which is explained by, and confirms, the fact that the disorder derives mainly from the interface rather than the volume of insulation).

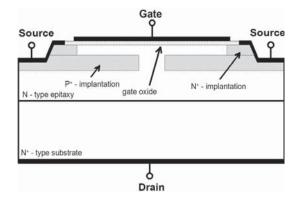

A third difference lies in the values of height barrier potential between the conduction bands of  $SiO_2$  and the semiconductor, which are much lower with SiC than with Si (the same is true among their valence bands), as shown in Figure 4.6. These values, which are reduced when the temperature increases, facilitate the

injection of carriers in the presence of an electric field. The undesirable consequences manifest in terms of the reliability of MOSFET structures, which is increasingly affected while the operating conditions are expected for use at high temperatures, and while this architecture of the component does not preserve the oxide from the large electric fields, that can handle silicon carbide. In addition, the current crystalline quality of substrates and epitaxies of SiC is probably still the cause of premature breakdowns of SiO<sub>2</sub> on SiC, under strong field and high temperature (as was formerly the case with silicon), also leading to reduced MOSFET structure lifetimes on SiC compared with those on silicon.

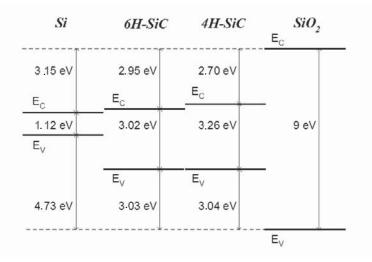

**Figure 4.6.** *Diagrams of energy band at 300 K for Si, SiC-6H, 4H-SiC and SiO*<sub>2</sub> showing the reduction in height of the barrier when the gap of the semiconductor increases, facilitating the injection of carriers into the insulation [AGA 97]

The physical nature of elements at the root of these electric events (for example, disorder at the interface, or low lifetime, etc.) is not fully clarified (for example, SiC crystal purity, clusters of carbon and surface roughness). A significant part of current research is trying to elucidate this [AFA 99] [AMY 01], and offers treatments [RAI 01] [KRA 01] in order to obtain a SiO<sub>2</sub> film quality compatible with the expected performance of power MOSFETs based on SiC. Without further delay, work is also focused on the architecture of the component itself, in order to circumvent this difficulty (examples will be provided later on in this chapter). At an intermediate level, some research, described below, is focused on alternative insulation that would allow the achievement of insulations for grid control or surface passivation better suited for SiC material.

#### 4.3.2.3.3. Other insulators

A triple stack of oxide and silicon nitride (ONO) is the only insulation currently discovered that leads to both a significant improvement in the threshold voltage, and in the lifetime at high temperature (ten days at 335°C) under a grid field of 2 MV/cm for MISFETs (horizontal structure on P epitaxy, with source and drain implanted in nitrogen). The breakdown electric field of the insulation is also higher (14 MV/cm) [LIP 00].

Some groups are interested in AlN, because of its dielectric permittivity which is similar to that of SiC, and a theoretical breakdown field in the same order of magnitude as SiO<sub>2</sub> (very high). AlN also has a good agreement of mesh with SiC, good thermal conductivity, and a good temperature strength. The maximum electric field of breakdown is currently measured at 3 MV/cm (by MOCVD filing), however, the experimental leakage currents remain prohibitive [LEL 00].

#### 4.3.2.4. Metallization

#### 4.3.2.4.1. Roles

During manufacturing of the component, metal depositions may take place (to make etching, or implantation masks, etc.). In the finished component, metals deposited on the semiconductor are intended to provide either an electrical connection with ohmic contact, or a junction via Schottky contact. Placed on top of an insulator, they can also take the role of the grid driving the switch; field plate, for the peripheral protection of a junction; or an interconnection path. We present here only the state of the art of features of ohmic contacts and Schottky on SiC, whose properties (e.g. height of barrier and thermal stability, etc.) are dependent on the state of the interface metal/SiC, and on the nature of metals and reactions.

#### 4.3.2.4.2. Schottky contacts and current features

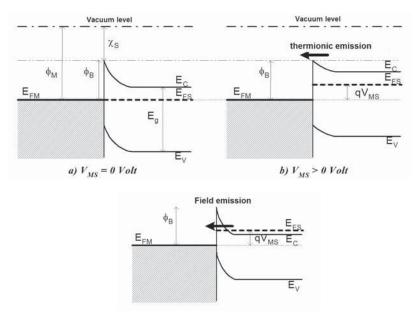

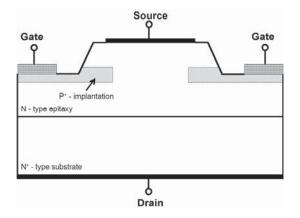

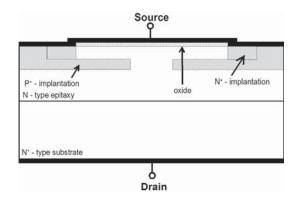

As recalled in Figure 4.7a, the junction between a metal and a semiconductor produces a potential barrier, called the Schottky barrier  $\Phi_B$ , which may display a rectifying behavior. A low doped semiconductor, moreover presenting a large gap, promotes obtaining a rectifier contact, also known as a Schottky contact (case of Figure 4.7b). In this way, many metals form a Schottky contact simply by layering upon SiC.

c)  $V_{MS} > 0$  Volt

Figure 4.7. Diagrams of energy band of a metal/semiconductor contact:

a) Ideal case of a Schottky barrier, such that Φ<sub>B</sub>=Φ<sub>B</sub>-χ<sub>S</sub>

b) Schottky contact on lightly doped n-type semiconductor: only the electrons able to overcome the barrier height will participate to the current flow

c) Ohmic contact on highly doped n-type semiconductor: electrons flow across the thin barrier by tunnel effect

The height of the barrier  $\Phi_B$  depends on the nature of the deposited metal, on the semiconductor (since ideally the barrier is equal to the difference between the work output of metal,  $\Phi_M$ , and the electronic affinity of the semiconductor,  $\chi_s$ , according to the Schottky-Mott relationship) and also on the chemical and structural condition of the semiconductor surface (of the polytype, its surface orientation – face C, face Si, or another face; the presence of a native oxide; or surface graphitization, etc.).

The experimental results show that  $\Phi_B$  depends on  $\Phi_M$  less than is expected by the theory. The summary of results on N-type, obtained in 1995 by Porter and Davis [POR 95], shows a range of values between 0.8 and 1.25 eV on SiC-6H (0001) – Si face, and between 1.0 and 1.6 eV on SiC-6H (0001) – C face, for all metals: Au, Al, Ag, Ti, Pd, Mn, Mg, Hf, Co, Ni. It was shown that the presence of surface conditions inside the forbidden energy band (intrinsic to the surface or induced by metallization) influences control of the Schottky barrier height, moderating the influence of output work. The semiconductor surface preparation stages before metal deposit, the parameters of this deposit and the quality of the SiC material are all crucial for the result and reproducibility of rectifier contact.

Ni is the most commonly used metal for the production of prototypes based on N-type rectifier contacts in 4H SiC because it has a high output work, leading to a barrier height of 1.24-1.29 eV on a 6H-SiC silicon face (after sacrificial oxidation of the surface and pre-annealing under ultra-vacuum [WAL 93]). Barrier height is equal to 1.6 eV on 4H-SiC (after chemical cleaning and cleaning *in-situ* before filing under ultra-vacuum), this increases by 0.23 eV after annealing at 700°C for 10 min; these works also relate to an ideal ratio of 1.1 [KES 00]. Titanium is the second most commonly used metal for obtaining Schottky contact on a N-type, leading to a rectifier contact coefficient ideally close to 1. The height of the barrier is 0.95 eV on 4H-SiC face Si (for a deposit after wet chemical cleanings) [ITO 97]. A change in barrier height, from 0.88 eV to 1.08 eV, was reported on 6H SiC-N-type after annealing at 700°C for 1 hour (linked to the changing nature of the interface metal [POR 95]).

The leakage currents in reverse polarization are higher than projected in the theory of simple thermo ionic emission. In addition to the possible participation of localized defects, or suburb effect, the contribution of a thermo ionic emission assisted by the field has been researched [HAT 02].

Works on SiC Schottky contacts of P-type are infrequent, given the rare need for this type of contact by applications. Barrier heights higher than those of the N-type are reported for SiC-6H (1.45 eV to 2.56 eV for Au, Ni, Pd, Al, Co, Ag, Ti, Cs, Mg face Si [ITO 97]), with ideal rectifier contact factors of greater than 1, showing that thermo ionic emission is not the predominant mechanism for conducting the current.

Current research is focused on optimizing manufacturing processes (by monitoring influence of surface pre-treatments [MOR 00], and type of metal [HAT 01], etc.), mainly in terms of temperature stability, quality and consistency on the large surface of the interface metal/SiC of P-type.

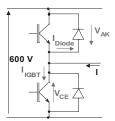

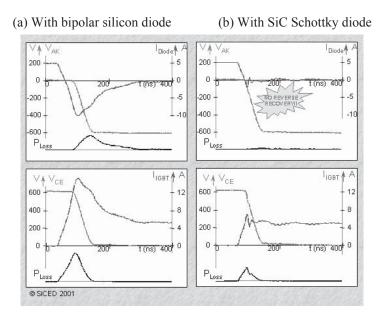

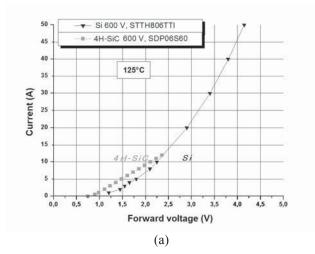

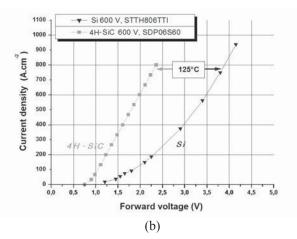

## 4.3.2.4.3. Ohmic contact and current features